AN-15-0015

作者: Tao Hu, Jiandong Liu

## 摘要

碳化硅场效应晶体管(SiC MOSFET)凭借高速开关特性,大幅降低开关损耗,目前已在各行业应用中加速渗透。然而,其器件特性所伴随的高 dV/dt(电压变化率),易引发寄生开通风险,已成为各行业应用设计中需重点规避的核心挑战。

本篇应用笔记聚焦自举供电场景,重点介绍一种 SiC MOSFET 的可靠驱动方案,通过将简易负压生成电路与具备米勒钳位功能的驱动芯片相结合,从而省去了专门的负压隔离电路设计。这一方案不仅简化了驱动电路架构,还显著减小PCB 布板面积,并有效降低系统成本。

#### 目录

| 1. 负压供电的主流方案比较     | 2  |

|--------------------|----|

| 2. 有源米勒钳位功能介绍      | 4  |

| 3. 米勒钳位叠加负压关断的典型应用 | 5  |

| 4. 米勒钳位叠加负压关断的效果   | 6  |

| 5. 负压生成电路中的选型计算    | 8  |

| 5.1. 稳态正负电压值的设定    | 8  |

| 5.2. 负压建立时间估算      | 9  |

| 5.3. 小占空比的稳态负压     | 9  |

| 6. 结语              | 9  |

| 7. 修订历史            | 10 |

#### 1.负压供电的主流方案比较

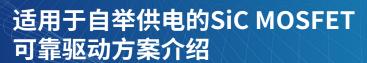

负压关断是一种常见的避免SiC MOSFET误导通的方式,而为栅极驱动芯片提供负压供电主要有两种方式。其一是通过隔离变压器产生独立的辅助电源,如下图所示:

图1.通过隔离变压器生成VEE的典型拓扑

其二是在SiC MOSFET的驱动回路上串联稳压管、电容、电阻等元器件,通过正常发波动作即可直接产生负压。

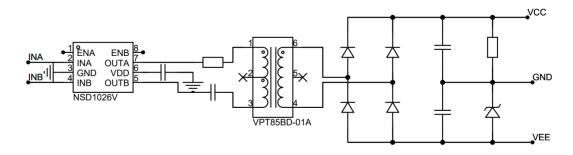

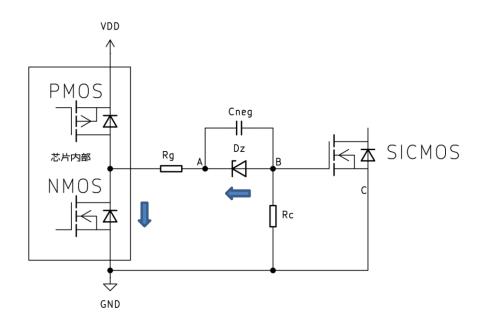

以下介绍这种负压发生的原理。如下图2所示,负压生成电路是由驱动电阻Rg,负压支撑电容 Cneg,负压钳位稳压管Dz,电流控制电阻Rc组成。其中控制电阻Rc直接并联于SiC MOSFET的 GS之间。

图2.负压生成电路的基本拓扑

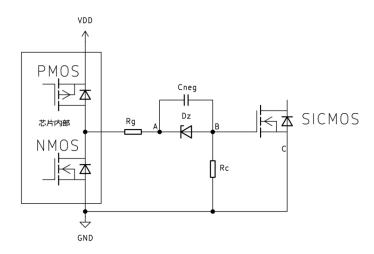

在芯片内部置高时,内部PMOS将芯片VDD短接至芯片OUT。此时如下图3,VDD通过驱动电阻 Rg、稳压管Dz与控制电阻Rc线路形成电流。此时Dz需要维持其在该电流下的钳位电压,Cneg的 B-A间将形成负压Vneg,SiC MOSFET的栅极电压值则为VDD-|Vneg|。

图3.负压生成电路置高时的工作原理

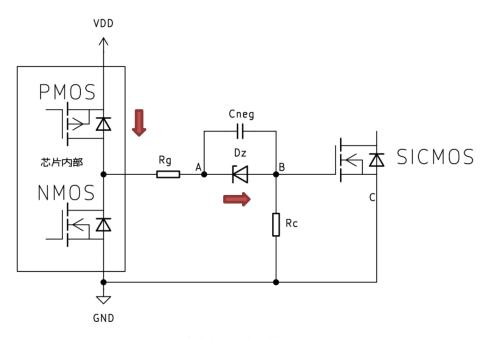

置低时内部NMOS将芯片GND短接至芯片OUT输出。此时如下图4,Cneg的A点通过芯片内部短路MOS对接至了SiC MOSFET栅极的负端,即C点。此时SiC MOSFET的栅极电压等于Cneg的B-A点间电压,即负压Vneg。

图4.负压生成电路置低时的工作原理

这种负压生成电路正常发波便能够使SiC MOSFET负压关断,自然地便可以用于低成本的自举供电。一个经典的通过自举方式便能够在高低边产生负压的拓扑如下图所示:

图5.一个典型的自举供电加负压生成电路的拓扑

相对于使用隔离变压器方式生成负压,这个简易负压生成电路有以下明显优势:

- 1, 省却了隔离变压器的单独供电回路, 可以有效降低系统成本;

- 2,省却了占板面积较大的变压器等元器件,有利于实现更为紧凑的布板设计;但在一些高dv/dt应用场景,如果SiC MOSFET仅采用负压关断仍然存在应用风险,此时就有必要将米勒钳位功能与负压关断相结合,从而实现最可靠的驱动方案

## 2.有源米勒钳位功能介绍

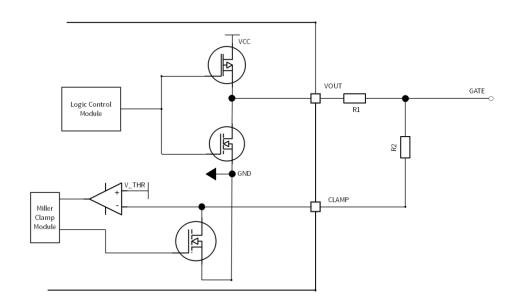

SiC MOSFET由于米勒效应造成寄生导通的机理是,在本管闭合时,对管开通,本管DS间的电压瞬变通过Cgd会对栅极GS间造成浪涌电流。由于本管所串联的栅极驱动电阻影响,使得SiC MOSFET的栅极电压瞬态越过了开通阈值造成误开通可能。而有源米勒钳位功能原理如下图6,芯片判断出本管闭合状态下(监测CLAMP与VEE管脚间电压低于V\_THR),会将栅极驱动电阻R1通过内部MOS短路,使得SiC MOSFET栅极的GS间阻抗极大降低,最终使浪涌电流造成的栅极电压摆幅明显降低。

图6.有源米勒钳位工作原理

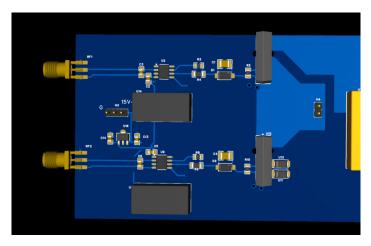

## 3.米勒钳位叠加负压关断的典型应用

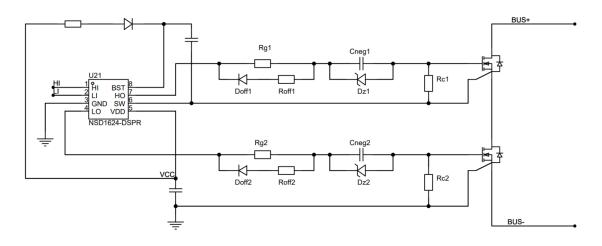

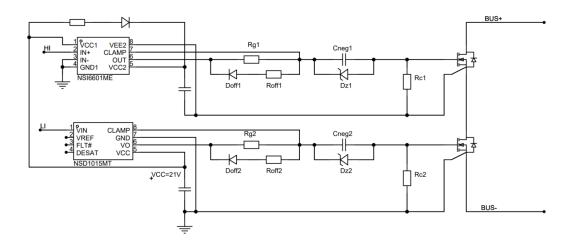

下图7展示了使用纳芯微低边驱动芯片NSD1015MT与隔离驱动芯片NSI6601ME芯片组合而成的半桥拓扑的典型驱动电路,该电路将有源米勒钳位引脚连接到稳压二级管的阳极,从而与负压生成电路叠加使用,可最大程度实现SiC MOSFET的可靠关断,并适用于各类反激、半桥、全桥等电源拓扑。

图7.负压生成电路在半桥应用的典型拓扑

NSI6601ME是最新一代集成米勒钳位功能的隔离驱动,具备出色的驱动性能和抗干扰能力。 NSD1015MT是单通道低边驱动,除有源米勒钳位外还具备DESAT功能,从而为SiC MOSFET提 供快速短路保护;故障上报引脚可向MCU实时反馈欠压、过流等故障信息,同时内部集成5V LDO 输出,可以为系统内其他芯片供电。注意,对3.3V的PWM信号输入,NSD1015MT需要前置一个 缓冲器芯片将信号转至5V。

#### 4.米勒钳位叠加负压关断的效果

为对比SiC MOSFE在高速开关下,驱动走线距离、负压关断、米勒钳位等影响因素对米勒效应的 影响,本文采用同样的驱动电阻大小(10欧姆),同款SiC MOSFET进行对比测试。该SiC MOSFET的栅极开通阈值Vth为最低2V,栅极电压最大安全工作区为-5V至22V——即栅极过冲电压 过高有误开通的风险,过低有损坏栅极的风险。下表是采用双脉冲测试,观测对管开关时,保持 关断状态的SiC MOSFET的栅极过冲情况汇总。

| 驱动走线<br>距离 | 负压关断<br>幅值 | 有源米勒<br>钳位 | 栅极正压<br>峰值 | 栅极负压<br>峰值 | 栅极电压<br>摆幅 | 风险       |

|------------|------------|------------|------------|------------|------------|----------|

| 10mm       | 0V         | 无          | 3.7V       | -4.8V      | 8.5V       | 误开通      |

| 10mm       | 0V         | 有          | 1.4V       | -2.0V      | 3.4V       | 临界安全     |

| 10mm       | -3V        | 无          | 0.9V       | -7.3V      | 8.2V       | 负压损坏     |

| 10mm       | -3V        | 有          | -0.7       | -4.2       | 3.5V       | 安全       |

| 30mm       | 0V         | 无          | 5.8V       | -5.9V      | 11.7V      | 误开通且负压损坏 |

| 30mm       | 0V         | 有          | 3.3V       | -2.8V      | 6.1V       | 误开通      |

| 30mm       | -3V        | 无          | 2.3V       | -9.2V      | 11.5V      | 误开通且负压损坏 |

| 30mm       | -3V        | 有          | 0.7V       | -5.8V      | 6.5V       | 负压损坏     |

表1.栅极驱动典型配置对比\*

#### 从上表中可以得出如下结论:

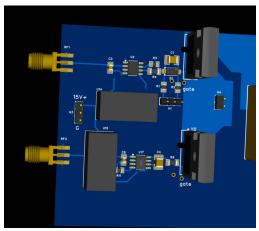

1,栅极驱动回路的layout走线长度在SiC MOSFET的米勒效应影响中占据非常大的权重。无论是 负压还是有源米勒钳位功能,在驱动回路走线很长的情况下,都很难使其过冲保留在栅极安全工 作电压范围内。因此在SiC MOSFET应用中,应尽量实现良好的驱动回路layout设计。

<sup>\*</sup>考虑到不同厂家不同型号的SiC MOSFET米勒比存在一定差异,同样条件下实测的米勒峰值电压 可能也会不同。

图8.PCB layout长引线(左)与短引线(右)的对比示意

- 2,在驱动回路走线良好的情况下,如果仅采用负压关断,由于米勒效应造成的正向震荡尖峰幅值降低,可以避免寄生导通;但由于震荡摆幅仍然很大,会造成负向震荡尖峰超出安全工作电压范围。

- 3,有源米勒钳位功能可以极大抑制米勒效应造成的栅极电压摆幅,如果仅使用有源米勒钳位功能与零压关断,在驱动回路走线良好的情况下可以做到正向震荡尖峰不超过SiC MOSFET开通阈值,达到临界安全工作状态;

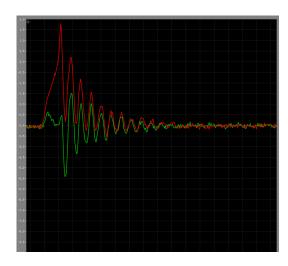

- 4,最佳方案是有源米勒钳位功能与负压关断措施同时使用,米勒钳位使得对管动作所造成的摆幅将被极大降低,同时负压的引入又能够将寄生上冲至开通阈值电压Vth的安全裕量控制于希望的位置,两者结合的效果将大于仅使用其中一种。由下图实测波形亦可以看出,若仅有负压,对管开通时依然有误开通风险,对管关断时产生的负压应力也更大。而同时施加了负压加米勒钳位功能后,效果远比单一措施更好。

图9.仅有负压(红)与负压加米勒钳位(绿)的实测波形对比 左图为对管开通时的波形,右图为对管分断时的波形

## 5.负压生成电路中的选型计算

根据上述分析,采用图7所介绍的自举驱动方案,将有源米勒钳位和负压关断电路相结合,可实现 对SiC MOSFET的可靠驱动。以下将对一个典型的负压生成电路做选型计算,以实现将栅极驱动的 正压维持于18V,负压维持于-3V左右的设计目标。

#### 5.1.稳态正负电压值的设定

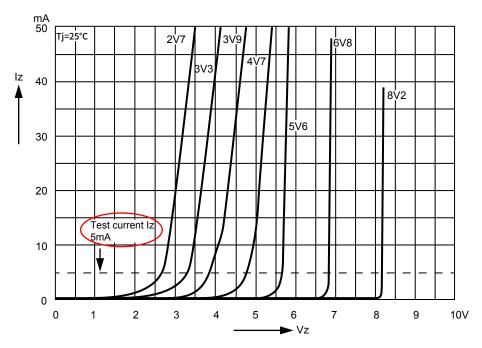

图7中的Rc即可控制Vneg的负压具体值。可通过型号稳压管对应的曲线来控制所需要稳定的负 压。如使用下图10中2V7型号的稳压管,想控制其电压于-2.7V,可看到其对应的Iz电流为5mA。 对于VDD=21V的电源电压,SiC MOSFET的栅极正压会是Von=VDD-|Vneg|=-

VDD-Vz=21V-2.7V=18.3V。根据图2原理,可令控制电阻Rc=Von/Iz=18.3V/5mA=3700 Ohm。 即Rc为3700欧姆时,可令负压维持在-2.7V。

Forward characteristics

图10.稳压二极管典型正向特性图

由于在每个功率管的开关周期,负压值会跳变,从而产生负压的纹波。如果Cneg的容值为SiC MOSFET的栅极电容量的N倍,则该跳变可估算为VDD/N。即N越大,跳变越可被忽略。也就是 说,此Cneg本身的容值越大,功率管开关所造成的纹波也就越小,一般推荐该N值大于250。

#### 5.2.负压建立时间估算

根据前述原理易知,只有在驱动芯片置高时才可以建立负压。驱动芯片输出置低时将维持该负压值。当置高时,VDD通过控制电阻Rc向Cneg充电至钳位电压Vz,负压达到稳定。即通过电流ic=(VDD-|Vneg|)/Rc为Cneg充电至Vneg,于是充电时间可表示为:t=|Vneg|\*Cneg/ic。对于刚才的设定,如果Cneg设定为1uF,则将Cneg从0V充电至-2.7V的电流为5mA,时间为2.7V\*1uF/5mA=540us。

在实际应用中,建议采用第一个PWM输出常高的方式为电容预充电,在负压稳定建立后再正常 发波。

#### 5.3.小占空比的稳态负压

在每个开关周期内,驱动芯片输出置高时负压电容被充电,驱动芯片输出置低时负压电容被放电。当占空比足够小时,芯片输出置高时Von为Cneg充电速度无法覆盖Voff时的放电速度,此时设定的Vneg会产生偏移,最终|Vneg|将维持在VDD\*D伏(开通周期与关断周期达到安秒平衡后可有Von\*D=|Vneg|\*(1-D),结合Von+|Vneg|=VCC,化简后可得|Vneg|=VDD\*D)。如5%占空比时,Vneg负压的值将无法维持于-2.7V,将会维持在-1V左右。由于该电路是将米勒钳位和负压关断叠加使用,因此-1V的关断负压仍然可以实现SiC MOSFET比较安全的关断。

#### 6.结语

本文通过将驱动芯片的有源米勒钳位功能和简易负压关断电路结合,设计了一种适用于自举供电的 SiC MOSFET可靠驱动方案。本文介绍了这个方案的基本原理和主要指标的设定方法,以及关键器件的选型方法,同时也通过实验比较展示了方案的优势。本方案介绍的简易负压关断电路可以实现自举供电,相比隔离供电产生负压,在简化设计和降低成本方面都有很大收益。

#### 7.修订历史

| 版本  | 描述     | 作者                   | 日期        |

|-----|--------|----------------------|-----------|

| 1.0 | 创建应用指导 | Tao Hu, Jiandong Liu | 2025/9/20 |

销售联系方式: sales@novosns.com; 获取更多信息: www.novosns.com

## 重要声明

本文件中提供的信息不作为任何明示或暗示的担保或授权,包括但不限于对信息准确性、完整性,产品适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的陈述或保证。

客户应对其使用纳芯微的产品和应用自行负责,并确保应用的安全性。客户认可并同意:尽管任何应用的相关信息或支持仍可能由纳芯微提供,但将在产品及其产品应用中遵守纳芯微产品相关的所有法律、法规和相关要求。

本文件中提供的资源仅供经过技术培训的开发人员使用。纳芯微保留对所提供的产品和服务进行更正、修改、增强、改进或其他更改的权利。纳芯微仅授权客户将此资源用于开发所设计的整合了纳芯微产品的相关应用,不视为纳芯微以明示或暗示的方式授予任何知识产权许可。严禁为任何其他用途使用此资源,或对此资源进行未经授权的复制或展示。如因使用此资源而产生任何索赔、损害、成本、损失和债务等,纳芯微对此不承担任何责任。

有关应用、产品、技术的进一步信息,请与纳芯微电子联系( www.novosns.com )。

苏州纳芯微电子股份有限公司版权所有