# 适用于激光雷达应用的 栅极驱动器Layout建议 AN-15-0014

作者: Xiaowen Jiang

## 摘要

激光雷达(Lidar)是一种用于精确测距的激光探测技术。栅极驱动器与GaN器件在最大化激光器发射能力上起到重要作用,为激光雷达带来更高的分辨率。NSD2017是一款适用于激光雷达应用的驱动器,具有强驱动能力、支持极窄脉宽输出以及强抗干扰能力的特点。本文从激光雷达的应用特点出发,介绍NSD2017在应用中PCB设计的注意点。

## 目录

| 1. 概要     | 2 |

|-----------|---|

| 2. 驱动回路   | 3 |

| 3. 回路寄生电感 | 4 |

| 4. 共源电感   | 5 |

| 5. 修订历史   | 7 |

### 1.概要

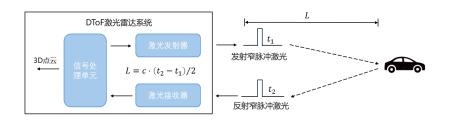

汽车自动驾驶中的激光雷达常采用DToF(Direct Time-of-Flight)测距方式,即通过直接测量激光的飞行时间进行距离测量和地图成像。图一是DToF激光雷达系统的典型结构,信号处理单元通过记录激光发射器发出光脉冲的时刻,以及激光接收器收到光脉冲的时刻,根据时间间隔和光速就可以计算出目标距离。

图1 DToF激光雷达系统典型结构

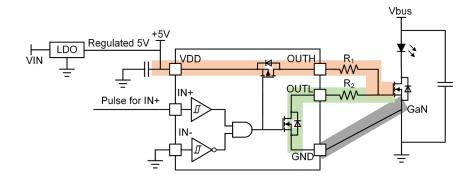

为实现高分辨率和宽监测范围,需要极窄的激光脉冲、极高的激光脉冲功率以及极高频开关频率,对激光发射器中的功率器件提出了较高的要求。相较于传统的Si MOSFET,GaN器件的快速开关速度以及高脉冲电流能力,非常适合DToF的应用,而GaN器件则需要对应的栅极驱动器进行驱动。以图2典型应用电路为例,低侧驱动器NSD2017驱动GaN器件为激光器提供高峰值电流。其中,激光脉冲越短,电流斜率要求越高,对PCB寄生电感的要求越高。本文从优化驱动回路出发,给出了NSD2017的PCB Layout建议。

图2 典型激光雷达驱动电路

### 2.驱动回路

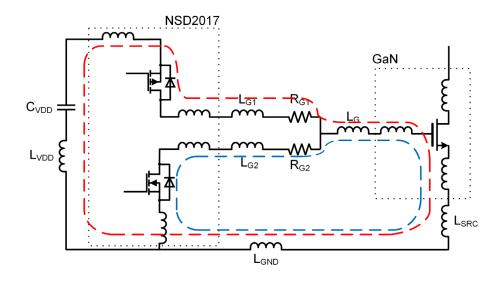

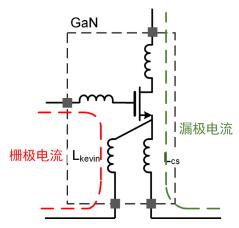

为减小栅极驱动回路寄生电感对驱动性能的影响,首先需要分析驱动器NSD2017开通和关断 GaN器件的回路。图3给出了栅极驱动回路的示意图。

红色曲线为驱动开通回路,当NSD2017输入信号转为高电平时,去耦电容正端经驱动器内部PMOS、驱动电阻至GaN HEMT的栅极,再由GaN HEMT的源极经地平面回到去耦电容负端。蓝色曲线为驱动关断回路,当NSD2017输入信号转为低电平时,电流经GaN HEMT栅极、驱动电阻、驱动器内部NMOS,再经驱动地平面回到GaN HEMT源极。

栅极回路电感的主要影响有以下几个方面: 1) 栅极回路电感直接影响开关性能,降低有效栅极驱动速率; 2) 栅极回路电感与GaN器件栅极电容形成谐振回路,将在GaN器件栅极产生过电压; 3) 谐振产生的驱动信号将导致器件误开关,这对低阈值电压的GaN器件影响尤为严重。

为减低寄生电感和器件栅极电容谐振的影响,一般会在驱动器输出增加驱动电阻,NSD2017分裂式输出的特点便于根据驱动开通和关断的谐振表现,灵活调整电阻阻值 $R_{G1}$ 和 $R_{G2}$ 。虽然调整驱动电阻可以解决驱动开关过程中遇到的振铃或误开关问题,但减缓了驱动开关速度,从而影响流经GaN HEMT的电流斜率,因此解决开关振铃的最好方法还是减小寄生电感。以此角度,可以从减小栅极回路电感和减小共源电感两个方向出发。

图3 栅极驱动回路示意图

### 3.回路寄生电感

以驱动开通回路为例,栅极回路的寄生自感可以认为由两部分组成:其一是由去耦电容至驱动器 VDD引脚的寄生电感 $L_{VDD}$ ,驱动器封装电感 $L_{N}$ ,驱动输出电感 $L_{G1}$ 和 $L_{G}$ ,GaN栅极封装电感组成,寄生电感大小与旁路电容、栅极驱动器和GaN的相对位置以及PCB的走线长短粗细有关;其二是由GaN源极封装电感,GaN源极PCB电感 $L_{SRC}$ 以及地回路电感 $L_{GND}$ 组成,与GaN封装设计、地回路的处理以及过孔的放置等影响。

#### 为减小驱动回路电感,有两个方向:

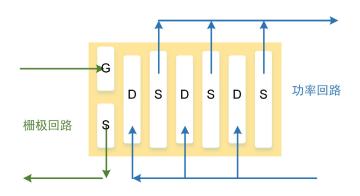

其一是减小驱动回路走线自感。建议使用短粗走线进行连接。由于面积相同的情况下,长走线的寄生电感大于细走线,长走线宽度增加一倍时,走线电感并不会减半。因此GaN器件与驱动器的相对位置摆放尤为重要。以下图为例,GaN器件栅极紧靠驱动器输出,驱动开通电流路径(蓝色)与返回电流路径(灰色)实现层间平行。

图4驱动器与GaN器件摆放

与栅极关断回路相比,开通回路的寄生电感的减小,还需要考虑电流流过高频去耦电容带来的影响。一般建议在NSD2017靠近供电引脚VDD附近放置大、小容值的两个电容,大容值电容一般为1-2uF用于保持VDD稳定,小容值电容一般为100nF-500nF用于滤除高频噪声。小容值电容使用短粗连线靠近放置VDD引脚附近,如果允许的话,建议使用低自感瓷片电容,如馈通电容等。

其二是合理利用磁通抵消原则减小寄生电感。比较简单的方式是,观察驱动开通电流路径和返回路径所围面积,面积越小,寄生电感越小。因此,电流返回路径选择开通电流路径紧邻的层,可以最大限度增加电感耦合实现最小化电感。

### 4.共源电感

栅极驱动电流路径和功率回路电流路径共用器件源极的寄生电感,这部分电感称为共源电感,一般由GaN 器件源极封装电感和源极PCB电感两部分组成。

共源电感同样需要最小化,且在激光雷达应用中最小化共源电感的优先级高于最小化栅极回路电感。当器件开通和关断过程中,共源电感在开关时刻产生与栅极驱动电压相反的电压,将减缓器件的开关过程,增大开关损耗,影响GaN的电流斜率,从而影响光脉宽信号。

为减小共源电感对驱动性能的影响,常利用开尔文连接方式将驱动回路和功率回路分开,以减小耦合。目前有商用GaN 器件中集成开尔文引脚,实现栅极电流回路与功率电流回路的解耦,消除了共源电感的影响。

图5 器件集成开尔文引脚以消除共源电感影响

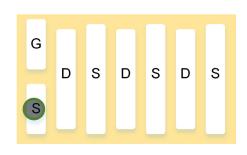

而目前较多低压GaN 器件没有开尔文引脚,可以通过PCB处理将功率回路和驱动回路分开。常见的处理方式如图6所示,选择靠近器件栅极的源极引脚作为驱动回路,其他引脚作为功率回路。

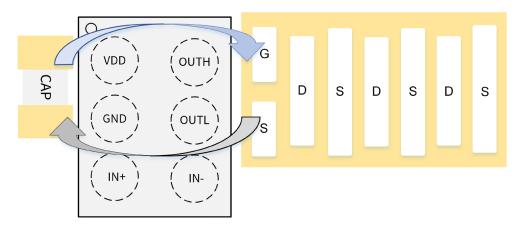

图6利用封装分开驱动回路和功率回路

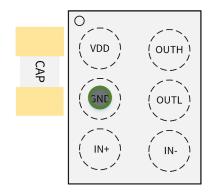

为实现最小共源电感,功率地与驱动地之间单点连接,建议将微过孔尽量靠近驱动器和功率器件摆放,如图7所示。

图7建议的微过孔摆放方式

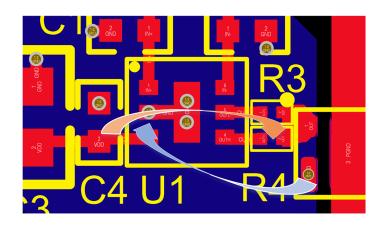

图8给出NSD2017一种常见的Layout设计,GaN器件中靠近Gate的Source中放置微孔,实现驱动地与功率地的单点连接,同时选用驱动开通电流相近层作为电流返回层,实现回路面积最小。(示例 Layout仅2层,用作说明)

图8 NSD2017推荐Layout

### 5.修订历史

| 版本  | 描述     | 作者            | 日期        |

|-----|--------|---------------|-----------|

| 1.0 | 创建应用笔记 | Xiaowen Jiang | 2025/9/10 |

销售联系方式: sales@novosns.com; 获取更多信息: www.novosns.com

### 重要声明

本文件中提供的信息不作为任何明示或暗示的担保或授权,包括但不限于对信息准确性、完整性,产品适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的陈述或保证。

客户应对其使用纳芯微的产品和应用自行负责,并确保应用的安全性。客户认可并同意:尽管任何应用的相关信息或支持仍可能由纳芯微提供,但将在产品及其产品应用中遵守纳芯微产品相关的所有法律、法规和相关要求。

本文件中提供的资源仅供经过技术培训的开发人员使用。纳芯微保留对所提供的产品和服务进行更正、修改、增强、改进或其他更改的权利。纳芯微仅授权客户将此资源用于开发所设计的整合了纳芯微产品的相关应用,不视为纳芯微以明示或暗示的方式授予任何知识产权许可。严禁为任何其他用途使用此资源,或对此资源进行未经授权的复制或展示。如因使用此资源而产生任何索赔、损害、成本、损失和债务等,纳芯微对此不承担任何责任。

有关应用、产品、技术的进一步信息,请与纳芯微电子联系( www.novosns.com )。

苏州纳芯微电子股份有限公司版权所有