### **NOVOSENSE**

# High-speed CAN Transceiver with Standby Mode

Datasheet (EN) 1.0

#### **Product Overview**

The NCA1044-Q1 is a high-speed CAN transceiver that provides an interface between a Controller Area Network (CAN) protocol controller and the physical two-wire CAN bus. The NCA1044-Q1 implements the CAN physical layer as defined in ISO 11898-2-2024 and SAE J2284-1 to SAE J2284-5. This implementation enables reliable communication in the CAN FD fast phase at data rates up to 5 Mbit/s. The NCA1044-Q1 provides thermal protection and transmit data dominant time out function.

### **Key Features**

- Fully compatible with the ISO11898-2 standard

- Ideal passive behavior to the CAN bus when the supply voltage is off

- I/O voltage range supports 1.8V, 3.3V and 5V MCU

- Power supply voltage

- V<sub>IO</sub>: 1.7V to 5.5V

- V<sub>CC</sub>: 4.5V to 5.5V

- Bus fault protection of -58V to +58V

- Bus common-mode voltage of -30V to +30V

- Transmit data (TXD) dominant time out function

- Very low-current Standby mode with wake-up capability

- Over temperature protection

- Data rate: up to 5Mbps

- Low loop delay: <250ns

- Operation temperature: -40°C to +125°C

- AEC-Q100 qualified for automotive, Grade 1

- RoHS & REACH compliant

### **Applications**

- CAN bus standards such as CANopen, DeviceNet, NMEA2000, ARNIC825, ISO11783 and CANaerospace

- Highly loaded CAN networks down to 10 kbps networks

- Automotive gateway

- Body control modules

- Advanced Driver Assistance Systems (ADAS)

- Infotainment system

#### **Device Information**

| Part Number    | Package | Body Size       |

|----------------|---------|-----------------|

| NCA1044-Q1SPR  | SOP8    | 4.90mm × 3.90mm |

| NCA1044-Q1DNR  | DFN8    | 3.00mm × 3.00mm |

| NCA1044N-Q1SPR | SOP8    | 4.90mm × 3.90mm |

| NCA1044N-Q1DNR | DFN8    | 3.00mm × 3.00mm |

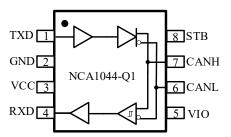

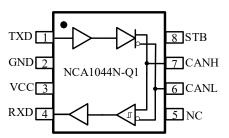

### **Functional Block Diagrams**

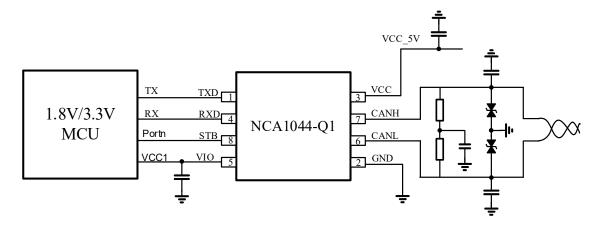

Figure 1. NCA1044-Q1 Block Diagram

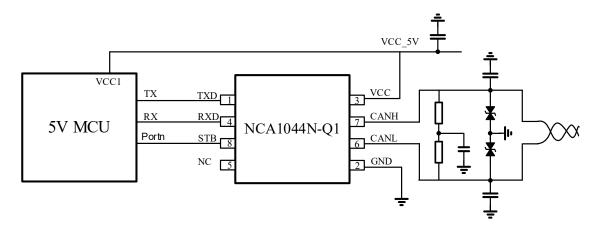

Figure 2. NCA1044N-Q1 Block Diagram

### **INDEX**

| 1. PIN CONFIGURATION AND FUNCTIONS    | 3  |

|---------------------------------------|----|

| 2. ABSOLUTE MAXIMUM RATINGS           | 4  |

| 3. EMC RATINGS                        | 4  |

|                                       |    |

| 4. RECOMMENDED OPERATING CONDITIONS   |    |

| 5. THERMAL INFORMATION                | 5  |

| 6. SPECIFICATIONS                     | 6  |

| 6.1. ELECTRICAL CHARACTERISTICS       | 6  |

|                                       | 9  |

|                                       |    |

|                                       |    |

| 7. FUNCTION DESCRIPTION               |    |

|                                       | 14 |

| 7.2. FUNCTIONAL BLOCK DIAGRAM         | 14 |

| 7.3. VIO SUPPLY PIN                   |    |

| 7.4. DEVICE OPERATING MODES           |    |

|                                       |    |

| ,                                     |    |

| 7.5. REMOTE WAKE-UP                   |    |

|                                       |    |

|                                       |    |

| · · · · · · · · · · · · · · · · · · · |    |

| •                                     |    |

| ·                                     |    |

| , ,                                   |    |

| 8. APPLICATION NOTE                   | 20 |

| 8.1. TYPICAL APPLICATION              | 20 |

| 9. PACKAGE INFORMATION                | 21 |

| 10. ORDERING INFORMATION              | 23 |

| 11. DOCUMENTATION SUPPORT             |    |

| 12. TAPE AND REEL INFORMATION         |    |

|                                       |    |

| 13. REVISION HISTORY                  |    |

# **1. Pin Configuration and Functions**

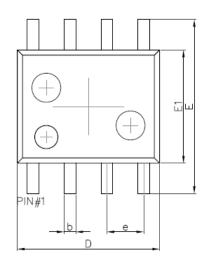

Figure 1-1 NCA1044-Q1, NCA1044N-Q1 Package

Table 1-1 NCA1044-Q1 Pin Configuration and Description

| NCA1044-Q1<br>PIN NO. | NCA1044N-Q1<br>PIN NO. | SYMBOL | FUNCTION                                                                     |

|-----------------------|------------------------|--------|------------------------------------------------------------------------------|

| 1                     | 1                      | TXD    | CAN transmit data input (LOW for dominant and HIGH for recessive bus states) |

| 2                     | 2                      | GND    | Ground                                                                       |

| 3                     | 3                      | VCC    | Power Supply                                                                 |

| 4                     | 4                      | RXD    | CAN receive data output (LOW for dominant and HIGH for recessive bus states) |

| 5                     | \                      | VIO    | Logic I/O supply voltage                                                     |

| \                     | 5                      | NC     | No connection                                                                |

| 6                     | 6                      | CANL   | Low-level CAN bus line                                                       |

| 7                     | 7                      | CANH   | High-level CAN bus line                                                      |

| 8                     | 8                      | STB    | STB (standby mode) select pin (active high)                                  |

# 2. Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)[1][2].

| Parameters                            | Symbol                                | Min  | Max | Unit |

|---------------------------------------|---------------------------------------|------|-----|------|

| Power Supply Voltage                  | VCC, VIO                              | -0.3 | 7   | ٧    |

| Logic I/O Voltage                     | TXD, RXD, STB                         | -0.3 | 7   | ٧    |

| Maximum bus Pin Voltage               | V <sub>CANH</sub> , V <sub>CANL</sub> | -58  | 58  | ٧    |

| Voltage between pin CANH and pin CANL | VCANH - VCANL                         | -58  | 58  | ٧    |

| Junction temperature                  | TJ                                    | -40  | 150 | °C   |

| Storage Temperature                   | $T_{stg}$                             | -65  | 150 | °C   |

<sup>[1]</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to Absolute Maximum Rating condition for extended periods may affect device reliability.

# 3. EMC Ratings

| Parameters              | Ratings                                                           | Value | Unit |

|-------------------------|-------------------------------------------------------------------|-------|------|

|                         | Human Body Model (HBM), per AEC-Q100-002                          |       |      |

|                         | CANH and CANL, to GND                                             | ±8    | kV   |

|                         | Other pins, to GND                                                | ±8    | kV   |

| Electrostatic discharge | Charged Device Model (CDM), per AEC-Q100-011                      |       |      |

|                         | All pins                                                          | ±2    | kV   |

|                         | Machine Model (MM), per JESD22-A115C                              |       |      |

|                         | All pins                                                          | ±400  | V    |

|                         | Electrical transient conduction, per ISO 7637-2, on CANH and CANL |       |      |

|                         | Pulse 1                                                           | -100  | V    |

| Electrical disturbances | Pulse 2a                                                          | 75    | V    |

|                         | Pulse 3a                                                          | -150  | V    |

|                         | Pulse 3b                                                          | 100   | V    |

<sup>&</sup>lt;sup>[2]</sup> All voltage values, except for "Voltage between pin CANH and pin CANL", are with respect to GND terminal.

# **4. Recommended Operating Conditions**

| Parameters                 | Symbol           | Min | Тур | Max | Unit |

|----------------------------|------------------|-----|-----|-----|------|

| Power Supply Voltage       | VCC              | 4.5 | 5   | 5.5 | V    |

| I/O Level-Shifting Voltage | VIO              | 1.7 | 3.3 | 5.5 | V    |

| Operating Temperature      | T <sub>opr</sub> | -40 | -   | 125 | °C   |

## 5. Thermal Information

| Parameters                                | Symbol               | SOP8 | DFN8 | Unit  |

|-------------------------------------------|----------------------|------|------|-------|

| IC Junction-to-Air Thermal Resistance     | $R_{\theta JA}$      | 120  | 52.8 | °C /W |

| Junction-to-case (top) thermal resistance | $R_{\theta JC(top)}$ | 57.8 | 58.9 | °C /W |

| Junction-to-board thermal resistance      | R <sub>θЈВ</sub>     | 64.2 | 25.2 | °C /W |

# 6. Specifications

### **6.1. Electrical Characteristics**

$V_{cc}$ =4.5V to 5.5V,  $V_{lo}$ =1.7 to 5.5V  $^{[1]}$ , Ta=-40°C to 125°C. Unless otherwise noted, Typical values are at  $V_{cc}$ =5V,  $V_{lo}$ =3.3V,  $R_L$ =60 $\Omega$ , Ta = 25°C.

| Symbol                | Parameters                       | Conditions                                                                                         | Min                 | Тур  | Max                  | Unit |

|-----------------------|----------------------------------|----------------------------------------------------------------------------------------------------|---------------------|------|----------------------|------|

| Supply; pir           | VCC                              |                                                                                                    |                     |      |                      |      |

| V <sub>cc</sub>       | Supply voltage                   |                                                                                                    | 4.5                 | -    | 5.5                  | ٧    |

|                       |                                  | Normal mode, recessive,<br>V <sub>TXD</sub> =V <sub>IO</sub> <sup>[2]</sup> , V <sub>STB</sub> =0V | -                   | 5    | 7                    | mA   |

|                       |                                  | Normal mode, dominant,<br>V <sub>TXD</sub> =0V                                                     | -                   | 45   | 60                   | mA   |

| Icc                   | Supply current                   | Normal mode, recessive,   -   5.5   V                                                              | mA                  |      |                      |      |

|                       |                                  |                                                                                                    | -                   | 0.7  | 2                    | μΑ   |

|                       |                                  |                                                                                                    | -                   | 13.5 | 20                   | μΑ   |

| V                     | Undervoltage detection           | Rising                                                                                             | 4                   | 4.26 | 4.5                  | V    |

| $V_{uvd(VCC)}$        | voltage on pin VCC               | Falling                                                                                            | 4                   | 4.17 | 4.5                  | ٧    |

| I/O level ad          | lapter supply; pin V10; only for | NCA1044-Q1                                                                                         |                     |      | •                    |      |

| V <sub>IO</sub>       | Supply voltage on pin VIO        |                                                                                                    | 1.7                 | -    | 5.5                  | V    |

|                       |                                  | Normal mode, recessive, V <sub>TXD</sub> =V <sub>IO</sub>                                          | -                   | 60   | 200                  | μΑ   |

| I <sub>IO</sub>       | Supply current on pin VIO        | Normal mode, dominant, V <sub>TXD</sub> =0V                                                        | -                   | 175  | 360                  | μΑ   |

|                       |                                  | Standby mode; V <sub>TXD</sub> =V <sub>IO</sub>                                                    | -                   | 11   | 19                   | μΑ   |

| .,                    | Undervoltage detection           | Rising                                                                                             | 1.4                 | 1.56 | 1.7                  | ٧    |

| V <sub>uvd(VIO)</sub> | voltage on pin VIO               | Falling                                                                                            | 1.4                 | 1.50 | 1.7                  | ٧    |

| Standby m             | ode control input; pin STB       |                                                                                                    |                     |      |                      | •    |

| .,                    |                                  | NCA1044-Q1                                                                                         | 0.7*V <sub>IO</sub> | -    | V <sub>IO</sub> +0.3 | ٧    |

| V <sub>IH</sub>       | High level input voltage         | NCA1044N-Q1                                                                                        | 2.0                 | -    | V <sub>cc</sub> +0.3 | ٧    |

| .,                    | Laurellaurellaurella             | NCA1044-Q1                                                                                         | -0.3                | -    | 0.3*V <sub>IO</sub>  | ٧    |

| V <sub>IL</sub>       | Low level input voltage          | NCA1044N-Q1                                                                                        | -0.3                | -    | 0.8                  | V    |

| R <sub>pu</sub>       | Pull-up resistance               |                                                                                                    | 40                  | 55   | 80                   | kΩ   |

| CAN transn            | nit data input; pin TXD          |                                                                                                    |                     |      | •                    |      |

| V <sub>IH</sub>       | High level input voltage         | NCA1044-Q1                                                                                         | 0.7*V <sub>IO</sub> | -    | V <sub>10</sub> +0.3 | ٧    |

|                     |                                              | NCA1044N-Q1                                                                                                                                        | 2.0     | -                   | V <sub>cc</sub> +0.3 | V  |

|---------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------|----------------------|----|

|                     |                                              | NCA1044-Q1                                                                                                                                         | -0.3    | -                   | 0.3*V <sub>IO</sub>  | ٧  |

| $V_{IL}$            | Low level input voltage                      | NCA1044N-Q1                                                                                                                                        | -0.3    | -                   | 0.8                  | ٧  |

| R <sub>pu</sub>     | Pull-up resistance                           |                                                                                                                                                    | 40      | 55                  | 80                   | kΩ |

| Ci                  | Input capacitance                            | [3]                                                                                                                                                | -       | 5                   | 10                   | pF |

| CAN recei           | ive data output; pin RXD                     |                                                                                                                                                    |         |                     |                      |    |

| Іон                 | High level output current                    | $V_{RXD} = V_{IO} - 0.4V^{[2]}$                                                                                                                    | -10     | -3.5                | -1                   | mA |

| I <sub>OL</sub>     | Low level output current                     | V <sub>RXD</sub> = 0.4V; bus dominant                                                                                                              | 1       | 3.5                 | 10                   | mA |

| Bus lines           | ; pins CANH and CANL; Driver                 |                                                                                                                                                    |         |                     |                      |    |

| $V_{OH(D)}$         | CANH output voltage (Dominant)               | $V_{TXD}$ =0V, $R_L$ =50 $\Omega$ to $65\Omega^{[4]}$                                                                                              | 2.75    | 3.6                 | 4.5                  | V  |

| $V_{OL(D)}$         | CANL output voltage (Dominant)               | $V_{TXD}$ =0V, $R_L$ =50 $\Omega$ to $65\Omega^{[4]}$                                                                                              | 0.5     | 1.4                 | 2.25                 | V  |

| $V_{OH(R)}$         | CANH output voltage                          | Normal mode, no load <sup>[4]</sup>                                                                                                                | 2.0     | 0.5*V <sub>cc</sub> | 3.0                  | V  |

| V OH(R)             | (Recessive)                                  | Standby mode, no load <sup>[4]</sup>                                                                                                               | -0.1    | -                   | 0.1                  | V  |

| $V_{OL(R)}$         | CANL output voltage                          | Normal mode, no load <sup>[4]</sup>                                                                                                                | 2.0     | 0.5*V <sub>cc</sub> | 3.0                  | V  |

| V OL(R)             | (Recessive)                                  | Standby mode, no load <sup>[4]</sup>                                                                                                               | -0.1    | -                   | 0.1                  | V  |

|                     |                                              | Normal mode                                                                                                                                        |         |                     |                      |    |

| $V_{\text{OD(D)}}$  | Differential output                          | $R_L = 50\Omega$ to $65\Omega^{[4]}$                                                                                                               | 1.5     | -                   | 3.0                  | ٧  |

| V OD(D)             | voltage (Dominant)                           | $R_L = 45\Omega$ to $70\Omega^{[4]}$                                                                                                               | 1.4     | -                   | 3.3                  | ٧  |

|                     |                                              | $R_L = 2240\Omega^{[4]}$                                                                                                                           | 1.5     | -                   | 5.0                  | ٧  |

| V                   | Differential output                          | Normal mode, no load <sup>[4]</sup>                                                                                                                | -50     | -                   | 50                   | mV |

| $V_{\text{OD(R)}}$  | voltage (Recessive)                          | Standby mode, no Load <sup>[4]</sup>                                                                                                               | -0.2    | -                   | 0.2                  | ٧  |

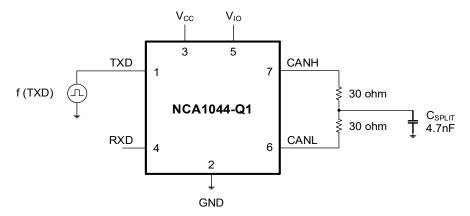

| $V_{TXsym}$         | Transmitter voltage symmetry                 | $V_{TXsym} = V_{CANH} + V_{CANL},$ [3] $f_{TXD} = 1 MHz,$ $R_L = 60\Omega, C_{SPLIT} = 4.7 nF,$ $V_{CC} = 4.75 V \text{ to } 5.25 V^{[4]}  ^{[5]}$ | 0.9*Vcc | -                   | 1.1*Vcc              | V  |

| I <sub>OSH(R)</sub> | CANH short-circuit output current, recessive | Normal mode,<br>V <sub>CANH</sub> = V <sub>CANL</sub> = -27V to 32V                                                                                | -2      | -                   | 2                    | mA |

| losl(R)             | CANL short-circuit output current, recessive | Normal mode,<br>V <sub>CANH</sub> = V <sub>CANL</sub> = -27V to 32V                                                                                | -2      | -                   | 2                    | mA |

| I <sub>OSH(D)</sub> | CANH short-circuit output current, dominant  | Normal mode,<br>V <sub>CANH</sub> = -15V to 40V, CANL open <sup>[4]</sup>                                                                          | -100    | -                   | 100                  | mA |

| hort-circuit output<br>t, dominant     | Normal mode, $V_{CANL} = -15V$ to 40V, CANH open <sup>[4]</sup>                                       | -100                       | -                       | 100                        | mA                            |

|----------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------|-------------------------|----------------------------|-------------------------------|

| and CANL; Receiver                     |                                                                                                       |                            |                         |                            | <b>,</b>                      |

| ntial input                            | -12V < V <sub>CANH</sub> <                                                                            | 12V, -12V < V              | / <sub>CANL</sub> < 12V |                            |                               |

| old voltage,                           | Normal mode <sup>[4]</sup>                                                                            | 0.5                        | -                       | 0.9                        | ٧                             |

| ve                                     | Standby mode <sup>[4]</sup>                                                                           | 0.4                        | -                       | 1.1                        | V                             |

|                                        | -12V < V <sub>CANH</sub> <                                                                            | 12V, -12V < V              | / <sub>CANL</sub> < 12V |                            | l                             |

| Differential input threshold voltage,  | Normal mode <sup>[4]</sup>                                                                            | 0.5                        | -                       | 0.9                        | V                             |

| ant                                    | Standby mode <sup>[4]</sup>                                                                           | 0.4                        | -                       | 1.1                        | V                             |

| ntial input<br>esis voltage            | -12V < V <sub>CANH</sub> < 12V,<br>-12V < V <sub>CANL</sub> < 12V,<br>Normal mode                     | -                          | 50                      | 100                        | mV                            |

|                                        | -12V < V <sub>CANH</sub> <                                                                            | 12V, -12V < V              | / <sub>CANL</sub> < 12V |                            |                               |

| Receiver recessive voltage             | Normal mode                                                                                           | -4                         | -                       | 0.5                        | V                             |

| -                                      | Standby mode                                                                                          | -4                         | -                       | 0.4                        | V                             |

|                                        | -12V < V <sub>CANH</sub> <                                                                            | 12V, -12V < V              | / <sub>CANL</sub> < 12V |                            |                               |

| er dominant<br>e                       | Normal mode                                                                                           | 0.9                        | -                       | 9                          | V                             |

|                                        | Standby mode                                                                                          | 1.15                       | -                       | 9                          | V                             |

| off (unpowered)<br>out leakage current | $V_{CANH} = V_{CANL} = 5V$ , $V_{CC} = V_{IO} = 0V^{[4]}$                                             | -10                        | -                       | 10                         | μΑ                            |

| esistance                              | $-2V \le V_{CANH} \le 7V,$ $-2V \le V_{CANL} \le 7V$ [3] [4]                                          | 25                         | 40                      | 50                         | kΩ                            |

| esistance matching                     | $V_{CANH} = 5V, V_{CANL} = 5V,$ $R_{I(match)} = 2*(R_{CANH} - R_{CANL})$ $/(R_{CANH} + R_{CANL})$ [3] | -1                         | -                       | 1                          | %                             |

| ntial input<br>nce                     | $-2V \le V_{CANH} \le 7V,$ $-2V \le V_{CANL} \le 7V,$ $R_{ID} = R_{CANH} + R_{CANL}$ [3] [4]          | 50                         | 80                      | 100                        | kΩ                            |

| apacitance to                          | CANH or CANL <sup>[3]</sup>                                                                           | -                          | -                       | 30                         | pF                            |

| ntial input                            | [3]                                                                                                   | -                          | -                       | 15                         | pF                            |

| l                                      |                                                                                                       | CANH OF CANL <sup>13</sup> | CANH OF CANL®           | CANH OF CANL <sup>ES</sup> | CANH OF CANL <sup>©3</sup> 30 |

| T <sub>SD</sub>      | Thermal shutdown threshold  | [3] | - | 193 | 1 | °C |

|----------------------|-----------------------------|-----|---|-----|---|----|

| T <sub>SD(hys)</sub> | Thermal shutdown hysteresis | [3] | - | 11  | - | °C |

<sup>[1]</sup> Only NCA1044-Q1 has a VIO pin. For NCA1044N-Q1, the VIO input is internally connected to VCC.

### **6.2. Switching Electrical Characteristics**

$V_{cc}$  =4.5V~5.5V,  $V_{lo}$ =1.7~5.5V<sup>[1]</sup>, Ta=-40°C to 125°C. Unless otherwise noted, Typical values are at  $V_{cc}$  = 5V,  $V_{lo}$  = 3.3V,  $R_L$ =60 $\Omega$ , Ta = 25°C.

| Symbol                             | Parameters                           | Comments                                                                  | Min | Тур | Мах | Unit |

|------------------------------------|--------------------------------------|---------------------------------------------------------------------------|-----|-----|-----|------|

| Driver                             |                                      |                                                                           |     |     |     |      |

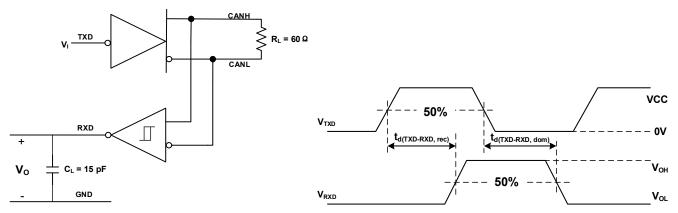

| $t_{\text{d(TXD-bus, dom)}}$       | Delay time from TXD to bus dominant  | Normal mode <sup>[3]</sup>                                                | -   | 40  | -   | ns   |

| $t_{\sf d(TXD-bus, rec)}$          | Delay time from TXD to bus recessive | Normal mode <sup>[3]</sup>                                                | -   | 65  | -   | ns   |

| +                                  | Transmitted recessive bit            | t <sub>bit(TXD)</sub> = 500 ns                                            | 435 | -   | 530 | ns   |

| t <sub>bit(bus)</sub>              | width width                          | $t_{bit(TXD)} = 200 \text{ ns}$                                           | 155 | -   | 210 | ns   |

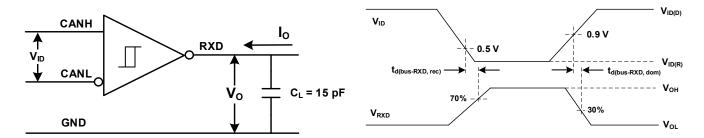

| Receiver                           |                                      |                                                                           |     |     |     |      |

| $t_{d(\text{bus-RXD},\text{dom})}$ | Delay time from bus to RXD dominant  | [3]                                                                       | -   | 90  | -   | ns   |

| $t_{\text{d(bus-RXD, rec)}}$       | Delay time from bus to RXD recessive | [3]                                                                       | -   | 80  | -   | ns   |

| $t_{d(TXD\text{-RXD}, dom)}$       | Delay time from TXD to RXD dominant  | Normal mode <sup>[3]</sup>                                                | -   | 130 | 255 | ns   |

| $t_{\text{d(TXD-RXD, rec)}}$       | Delay time from TXD to RXD recessive | Normal mode <sup>[3]</sup>                                                | -   | 145 | 255 | ns   |

|                                    | D                                    | $t_{bit(TXD)} = 500 \text{ ns}$                                           | 400 | -   | 550 | ns   |

| t <sub>bit(RXD)</sub>              | Bit time on pin RXD                  | t <sub>bit(TXD)</sub> = 200 ns                                            | 120 | -   | 220 | ns   |

| CAN FD timi                        | ng characteristics                   |                                                                           |     |     |     |      |

|                                    |                                      | $\Delta t_{\text{rec}} = t_{\text{bit(RXD)}} - t_{\text{bit(bus)}}^{[3]}$ |     |     |     |      |

| $\Delta t_{\text{rec}}$            | Receiver timing symmetry             | $t_{bit(TXD)} = 500 \text{ ns}$                                           | -65 | -   | 40  | ns   |

|                                    |                                      | t <sub>bit(TXD)</sub> = 200 ns                                            | -45 | -   | 15  | ns   |

| Dominant t                         | ime-out time; pin TXD                |                                                                           |     |     |     |      |

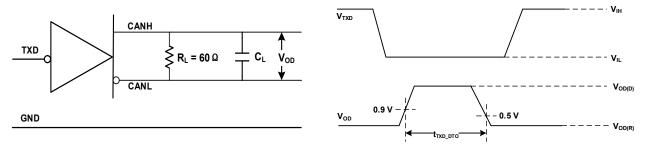

| $t_{\text{to(dom)TXD}}$            | TXD dominant time-out time           | Normal mode <sup>[3]</sup>                                                | 0.8 | 2.8 | 5   | ms   |

$<sup>^{[2]}</sup>$   $V_{IO}$ = $V_{CC}$  for the version without VIO pin.

<sup>[3]</sup> Not tested in production; guaranteed by design.

<sup>[4]</sup> Required in ISO 11898-2-2024.

<sup>[5]</sup> The test circuit used to measure the bus output voltage symmetry (which includes C<sub>SPLIT</sub>) is shown in Figure 6-3.

| Bus wake-up time; pins CANH, CANL |                                   |                                 |     |   |     |    |  |

|-----------------------------------|-----------------------------------|---------------------------------|-----|---|-----|----|--|

| t <sub>wake(bus, dom)</sub>       | Bus dominant wake-up time         | Standby mode <sup>[2] [3]</sup> | 0.5 | - | 1.8 | μs |  |

| twake(bus, rec)                   | Bus recessive wake-up time        | Standby mode <sup>[2] [3]</sup> | 0.5 | - | 1.8 | μs |  |

| t <sub>to(wake)bus</sub>          | Bus wake-up time out              | Standby mode <sup>[2] [3]</sup> | 0.8 | - | 9   | ms |  |

| t <sub>fltr(wake)bus</sub>        | Bus wake-up filter time           | Standby mode <sup>[2] [3]</sup> | -   | - | 1.8 | μs |  |

| Mode transition                   |                                   |                                 |     |   |     |    |  |

| t <sub>d(stb-norm)</sub>          | Standby to normal mode delay time | [2]                             | -   | - | 47  | μs |  |

$<sup>^{[1]}</sup>$  Only NCA1044-Q1 has a VIO pin. For NCA1044N-Q1, the VIO input is internally connected to VCC.

$<sup>\</sup>sp[2]$  Not tested in production; guaranteed by design.

<sup>[3]</sup> Required in ISO 11898-2-2024.

#### **6.3. Parameter Measurement Information**

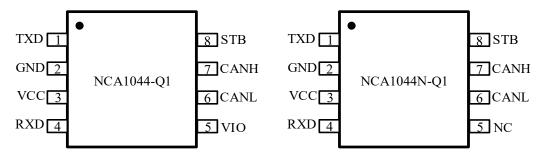

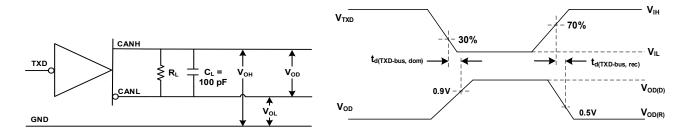

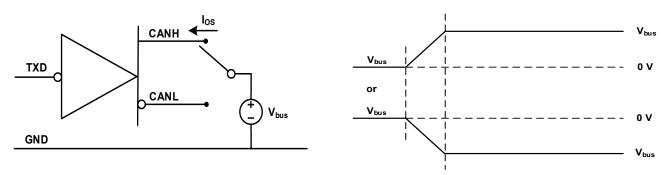

Figure 6-1 Driver Test Circuit and Voltage Waveforms<sup>[1]</sup>

Figure 6-2 Receiver Test Circuit and Voltage Waveforms

Figure 6-3 Transceiver Driver Symmetry Test Circuit

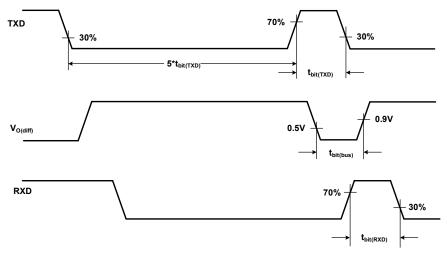

Figure 6-4 Loop Time Test Circuit and Voltage Waveforms

Figure 6-5 TXD Dominant Time-out Test Circuit and Voltage Waveforms

Figure 6-6 Driver Short-Circuit Current Test Circuit and Waveforms

Figure 6-7  $t_{\text{bit}(\text{RXD})}$  Test Circuit and Waveforms  $^{\![1]}$

$<sup>^{[1]}</sup>$  For NCA1044N-Q1, TXD high level is set as 2.0V instead, and TXD low level 0.8V instead.

### 7. Function Description

#### 7.1. Overview

The NCA1044-Q1 is a CAN transceiver which fully compatible with the ISO11898-2 standard. The data rate of the NCA1044-Q1 is up to 5Mbps, and it can support up to 110 CAN nodes. Meanwhile, the maximum transmission rate of the CAN bus is limited by the bus load, the quantity of nodes, the cable length, and other factors. The NCA1044-Q1 has a ±30V input common-mode range, enabling reliable communication between bus nodes with large ground potential deviations. NCA1044-Q1 has a low-current standby mode with CAN BUS waked-up capability.

Comprehensive protection features are designed to enhance the device and network robustness in harsh operating conditions. The transmit data dominant time-out function prevents the bus from lock-up by the faults on micro-controller. Moreover, the NCA1044-Q1 provides thermal protection and short-circuit protection.

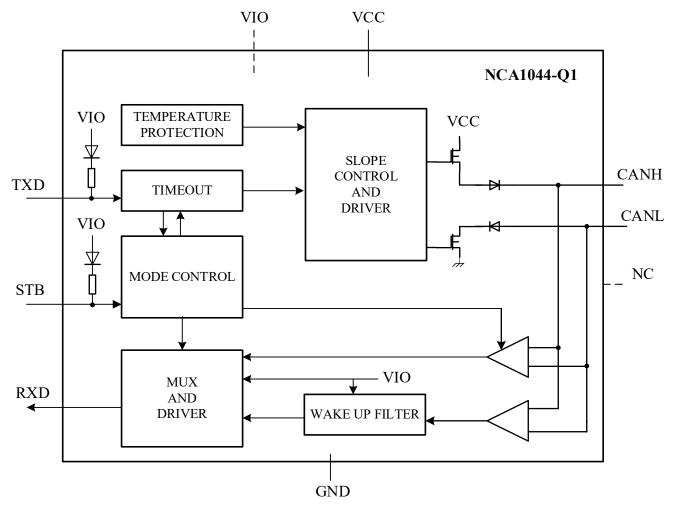

### 7.2. Functional Block Diagram

Figure 7-1 Block diagram of NCA1044-Q1

#### 7.3. VIO Supply Pin

Two versions of the NCA1044-Q1 are available, only differing in the function of a single pin. Pin 5 is either a VIO supply pin or a NC pin.

Pin VIO should be connected to the microcontroller supply voltage (see Figure 8-1). This will adjust the signal levels of pins TXD, RXD and STB to the I/O levels of the microcontroller. Pin VIO also provides the internal supply voltage for the low-power differential receiver of the transceiver. For applications running in low-power mode, this allows the bus lines to be monitored for activity even if there is no supply voltage on pin VCC.

For versions of the NCA1044N-Q1 without a VIO pin, the VIO input is internally connected to VCC. This sets the signal levels of pins TXD, RXD and STB to levels compatible with 5 V microcontrollers.

#### 7.4. Device Operating Modes

The device has two main operating modes: Normal mode and Standby mode. Operating mode is selected via the STB input pin. Table 7-1 shows a description of the operating modes under normal supply conditions.

| Mode    | STB pin | TXD pin | CAN driver | RXD pin                          |

|---------|---------|---------|------------|----------------------------------|

|         |         | LOW     | dominant   | LOW                              |

| Normal  | LOW     | HIGH    | recessive  | LOW when bus dominant            |

|         |         |         |            | HIGH when bus recessive          |

| Charadh | -dh-    |         | CND        | Follow bus when wake-up detected |

| Standby | HIGH    | X       | GND        | HIGH when no wake-up detected    |

Table 7-1 Operating Modes

#### 7.4.1. Normal Mode

A LOW level on pin STB selects Normal mode. In this mode, the transceiver can transmit and receive data via the bus lines CANH and CANL (see Figure 7-1). The differential receiver converts the analog data on the bus lines into digital data which is output to pin RXD. The slopes of the output signals on the bus lines are controlled internally and are optimized in a way that guarantees the lowest possible Electromagnetic Emission (EME).

After entering normal mode, it is recommended to firstly pull up TXD pin to a high level for at least 200ns before communications, for fear of unwanted TXD timeout caused by unstable TXD level during the power-on phase.

#### 7.4.2. Standby Mode

A HIGH level on pin STB selects Standby mode. In Standby mode, the transceiver is not able to transmit or correctly receive data via the bus lines. The transmitter and Normal-mode receiver blocks are switched off to reduce supply current, and only a low-power differential receiver monitors the bus lines for activity. The wake-up filter on the output of the low-power receiver does not latch bus dominant states, but ensures that only bus dominant and bus recessive states that persist longer than tftr(wake)bus are reflected on pin RXD.

In Standby mode, the bus lines are biased to ground to minimize the system supply current. The low-power receiver is supplied by  $V_{10}$ , and is capable of detecting CAN bus activity even if  $V_{10}$  is the only supply voltage available. When pin RXD goes LOW to signal a wake-up request, a transition to Normal mode will not be triggered until STB is forced LOW.

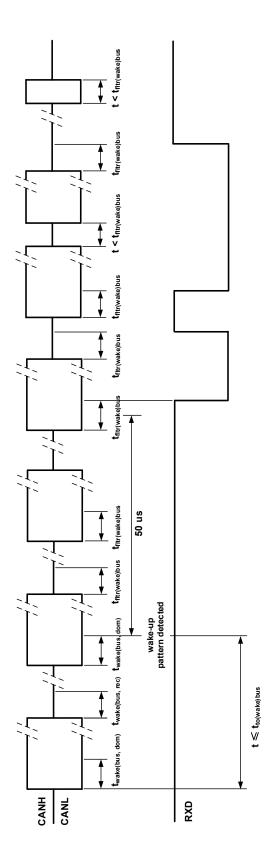

#### 7.5. Remote Wake-up

The NCA1044-Q1 wakes up from Standby mode when a dedicated wake-up pattern is detected on the bus (see Figure 7-2). This filtering helps avoid spurious wake-up events. A spurious wake-up sequence could be triggered by, for example, a dominant clamped bus or by dominant phases due to noise or spikes on the bus. The wake-up pattern must have a complete dominant-recessive-dominant pattern, in which the dominant phase at least has twake(bus, dom) and the recessive phase at least has twake(bus, rec), otherwise it will be ignored.

### NCA1044-Q1

The complete dominant-recessive-dominant pattern must be received within  $t_{to(wake)bus}$  to be recognized as a valid wake-up pattern. Otherwise, the internal wake-up logic is reset. The complete wake-up pattern will then need to be retransmitted to trigger a wake-up event. Pin RXD remains HIGH until the wake-up event has been triggered.

After a wake-up sequence has been detected, the NCA1044-Q1 will remain in Standby mode with the bus signals reflected on RXD after 50 $\mu$ s. During this 50 $\mu$ s, the low-power receiver is on but pin RXD is not active (i.e. HIGH/recessive). The first dominant pulse width  $\geq t_{fltr(wake)bus}$  that ends after the 50 $\mu$ s will trigger RXD to go LOW/dominant. Note that dominant or recessive phases lasting less than  $t_{fltr(wake)bus}$  will not be detected by the low-power differential receiver and will not be reflected on RXD in Standby mode.

A wake-up event is not flagged on RXD if any of the following events occurs while a valid wake-up pattern is being received:

- The NCA1044-Q1 switches to Normal mode.

- The complete wake-up pattern was not received within tto(wake)bus.

- A VCC or VIO undervoltage is detected (VCC < V<sub>uvd(VCC)</sub> or VIO < V<sub>uvd(VIO)</sub>; see Section 7.6.3).

Figure 7-2 Wake-Up Timing

#### 7.6. Fail-safe features

#### 7.6.1.TXD Dominant Time-Out Function (TXD DTO)

A 'TXD dominant time-out' timer circuit prevents the bus lines from being driven to a permanent dominant state (blocking all network communication) if pin TXD is forced permanently LOW by a hardware and/or software application failure. The timer is triggered by a negative edge on pin TXD.

If the duration of the LOW level on pin TXD exceeds the internal timer value  $t_{to(dom)TXD}$ , the transmitter is disabled, driving the bus lines into a recessive state. The timer is reset by a positive edge on pin TXD. The TXD dominant time-out time also defines the minimum possible bit rate of 10 kbit/s.

#### 7.6.2. Internal Biasing of TXD and STB Input Pins

Pins TXD and STB have internal pull-ups to VIO to ensure a safe, defined state, in case one or both of these pins are left floating. Pull-up currents flow in these pins in all states; both pins should be held HIGH in Standby mode to minimize standby current.

#### 7.6.3. Undervoltage Detection on Pins VCC and VIO

The supply terminals have undervoltage detection that places the device in protected mode. This protects the bus during an undervoltage event on either the VCC or VIO supply terminals. When VCC drop below the VCC undervoltage detection level, V<sub>uvd(VCC)</sub>, the transceiver will switch to Standby mode. The logic state of pin STB will be ignored until VCC has recovered. When VIO drop below the VIO undervoltage detection level, V<sub>uvd(VIO)</sub>, the transceiver will switch off and disengage from the bus (zero load) until VIO has recovered.

After an undervoltage condition is cleared and the supplies have returned to valid levels, the device typically resumes normal operation within 50 µs.

| Tubic                | Table 1 2 officer voltage Lockout 3V offig Devices (No.110++11 Q1) |                   |                            |  |  |  |

|----------------------|--------------------------------------------------------------------|-------------------|----------------------------|--|--|--|

| VCC                  | <b>Device State</b>                                                | <b>Bus Output</b> | RXD                        |  |  |  |

| >UV <sub>VCC</sub>   | Normal                                                             | Per TXD           | Mirrors Bus <sup>[1]</sup> |  |  |  |

| <uv<sub>vcc</uv<sub> | Off                                                                | High Impedance    | High Impedance             |  |  |  |

Table 7-2 Undervoltage Lockout 5V Only Devices (NCA1044N-O1)

Table 7-3 Undervoltage Lockout I/O Level Shifting Devices (NCA1044-Q1)

| VCC                  | VIO                  | Device State | Bus Output     | RXD                                 |

|----------------------|----------------------|--------------|----------------|-------------------------------------|

| >UV <sub>vcc</sub>   | >UV <sub>VIO</sub>   | Normal       | Per TXD        | Mirrors Bus <sup>[1]</sup>          |

| <uv<sub>vcc</uv<sub> | >UV <sub>VIO</sub>   | Standby Mode | GND            | Bus Wake RXD Request <sup>[2]</sup> |

| >UV <sub>vcc</sub>   | <uv<sub>VIO</uv<sub> | Off          | High Impedance | High Impedance                      |

| <uv<sub>vcc</uv<sub> | <uv<sub>VIO</uv<sub> | Off          | High Impedance | High Impedance                      |

<sup>[1]</sup> Mirrors bus state: low if CAN bus is dominant, high if CAN bus is recessive.

#### 7.6.4. Unpowered Device

The device is designed to be 'ideal passive' or 'no load' to the CAN bus if it is unpowered. The bus terminals (CANH, CANL) have extremely low leakage currents when the device is unpowered to avoid loading down the bus. This is critical if some nodes of the network are unpowered while the rest of the of network remains in operation. The logic terminals also have extremely low leakage currents when the device is unpowered to avoid loading down other circuits that may remain powered.

#### 7.6.5. Over-Temperature Protection (OTP)

The output drivers are protected against over-temperature conditions. If the virtual junction temperature exceeds the shutdown junction temperature T<sub>SD</sub>, the output drivers will be disabled until the virtual junction temperature becomes lower than T<sub>SD</sub> and TXD

<sup>[1]</sup> Mirrors bus state: low if CAN bus is dominant, high if CAN bus is recessive.

<sup>[2]</sup> Refer to Section 7.5.

# NCA1044-Q1

becomes recessive again. By including the TXD condition, the occurrence of output driver oscillation due to temperature drifts is avoided.

## 8. Application Note

### 8.1. Typical Application

The NCA1044-Q1 requires a  $0.1 \,\mu\text{F}$  bypass capacitors between VCC and GND. The capacitor should be placed as close as possible to the package. The Figure 8-1 and Figure 8-2 are the typical applications of NCA1044-Q1.

Figure 8-1 Typical CAN Bus Application Using 1.8V/3.3V CAN Controller

Figure 8-2 Typical CAN Bus Application Using 5V CAN Controller

# 9. Package Information

| Symbol | Dimensions In Millimeters |       | Dimensions In Inches |       |

|--------|---------------------------|-------|----------------------|-------|

| Symbol | Min.                      | Max.  | Min.                 | Max.  |

| Α      | 1.450                     | 1.750 | 0.057                | 0.069 |

| A1     | 0.100                     | 0.250 | 0.004                | 0.010 |

| A2     | 1.350                     | 1.550 | 0.053                | 0.061 |

| b      | 0.330                     | 0.510 | 0.013                | 0.020 |

| С      | 0.170                     | 0.250 | 0.007                | 0.010 |

| D      | 4.700                     | 5.100 | 0.185                | 0.201 |

| Е      | 5.800                     | 6.200 | 0.228                | 0.244 |

| E1     | 3.800                     | 4.000 | 0.150                | 0.157 |

| е      | 1.270(BSC)                |       | 0.050(               | (BSC) |

| L      | 0.400                     | 1.270 | 0.016                | 0.050 |

| θ      | 0°                        | 8°    | 0°                   | 8°    |

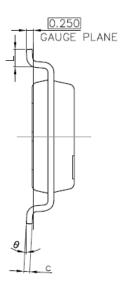

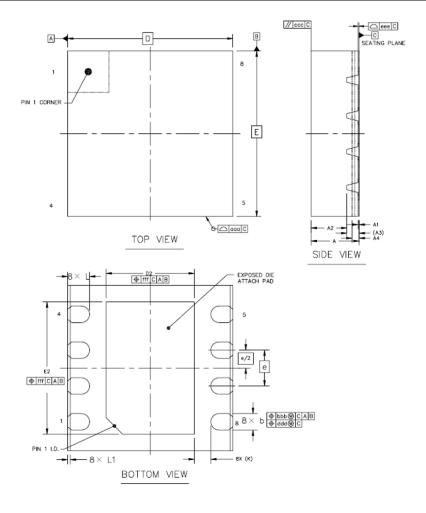

Figure 9-1 SOP8 Package Shape and Dimension

|                    |     |                                                                     |          | MAX    |

|--------------------|-----|---------------------------------------------------------------------|----------|--------|

| TOTAL THICKNESS    |     | 0.80                                                                | 0.85     | 0.90   |

| STAND OFF          |     | 0                                                                   | 0.02     | 0.0500 |

|                    | A2  |                                                                     | 0.6      |        |

|                    | A3  | 0.203 REF                                                           |          |        |

|                    | A4  | 0.075                                                               |          | 0.18   |

| X                  | D   | 3 BSC                                                               |          |        |

| Y                  | Ε   | 3 BSC                                                               |          |        |

|                    | ь   | 0.25                                                                | 0.30     | 0.35   |

|                    | e   |                                                                     | 0.65 BSC |        |

| Х                  | D2  | 1.5                                                                 | 1.6      | 1.7    |

| Y                  | E2  | 2.3                                                                 | 2.4      | 2.5    |

|                    | L   | 0.35                                                                | 0.4      | 0.45   |

|                    | L1  | 0.01                                                                |          | 0.09   |

| D EDGE             | к   | 0.3 REF                                                             |          |        |

| E                  | aaa | 0.1000                                                              |          |        |

|                    | ccc | 0.1000                                                              |          |        |

|                    | eee | 0.0800                                                              |          |        |

|                    | bbb | 0.1000                                                              |          |        |

| LEAD OFFSET        |     | 0.0500                                                              |          |        |

| EXPOSED PAD OFFSET |     | 0.1000                                                              |          |        |

|                    |     |                                                                     |          |        |

|                    |     |                                                                     |          |        |

|                    | Y   | A3  A4  X D  Y E  b  e  X D2  Y E2  L  L1  D EDGE K  E aga  ccc eee | A2       | A2     |

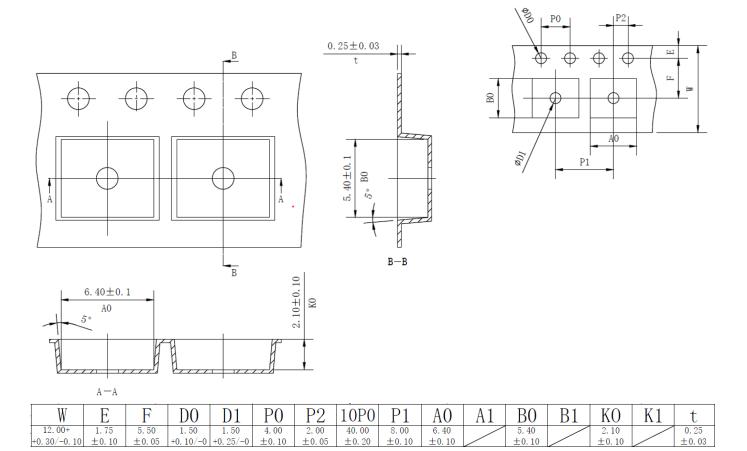

Figure 9-2 DFN8 Package Shape and Dimension

# 10. Ordering Information

| Part Number    | Operation<br>Temperature | MSL | Package<br>Type | SPQ  |

|----------------|--------------------------|-----|-----------------|------|

| NCA1044-Q1SPR  | -40 to 125°C             | 3   | SOP8            | 2500 |

| NCA1044-Q1DNR  | -40 to 125°C             | 2   | DFN8            | 6000 |

| NCA1044N-Q1SPR | -40 to 125°C             | 3   | SOP8            | 2500 |

| NCA1044N-Q1DNR | -40 to 125°C             | 2   | DFN8            | 6000 |

# 11. Documentation Support

| Part Number | Product Folder | Datasheet  | Technical Documents |

|-------------|----------------|------------|---------------------|

| NCA1044-Q1  | Click here     | Click here | Click here          |

# 12. Tape and Reel Information

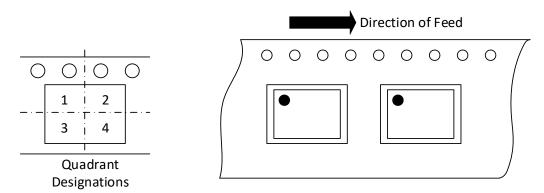

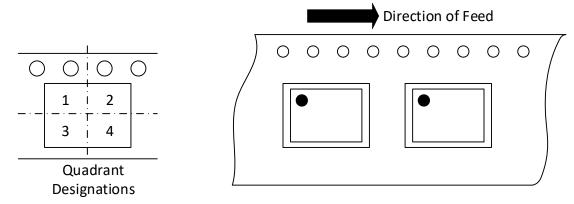

Figure 12-1 Tape Information of SOP8

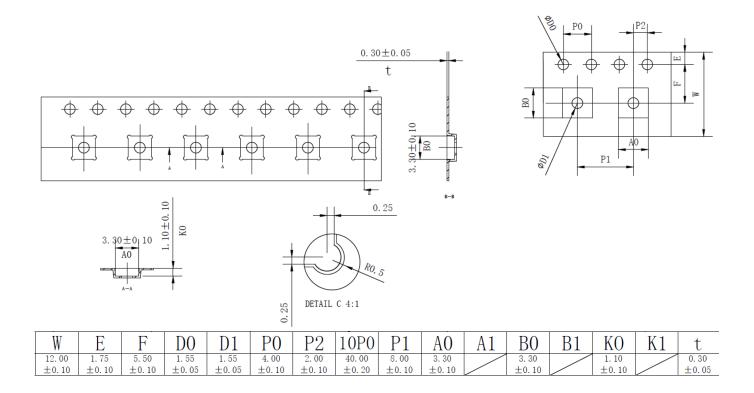

Figure 12-2 Tape Information of DFN8

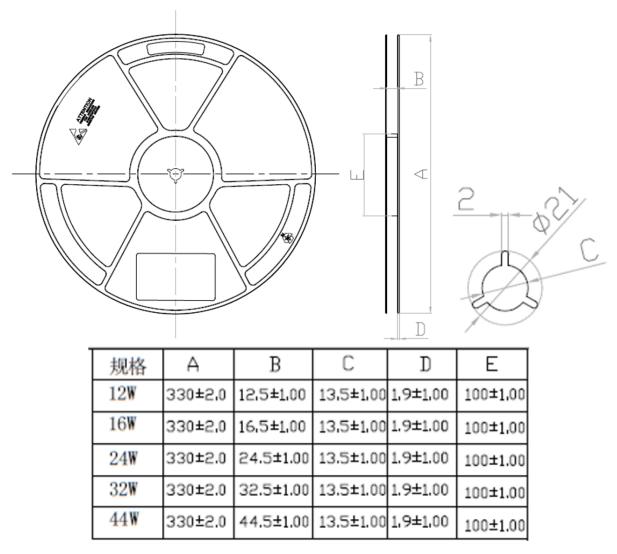

Figure 12-3 Reel Information of SOP8 and DFN8

## 13. Revision History

| Revision | Description      | Date      |

|----------|------------------|-----------|

| 1.0      | Initial Version. | 2024/9/30 |

#### **IMPORTANT NOTICE**

The information given in this document (the "Document") shall in no event be regarded as any warranty or authorization of, express or implied, including but not limited to accuracy, completeness, merchantability, fitness for a particular purpose or infringement of any third party's intellectual property rights.

Users of this Document shall be solely responsible for the use of NOVOSENSE's products and applications, and for the safety thereof. Users shall comply with all laws, regulations and requirements related to NOVOSENSE's products and applications, although information or support related to any application may still be provided by NOVOSENSE.

This Document is provided on an "AS IS" basis and is intended only for skilled developers designing with NOVOSENSE' products. NOVOSENSE reserves the rights to make corrections, modifications, enhancements, improvements or other changes to the products and services provided without notice. NOVOSENSE authorizes users to use this Document exclusively for the development of relevant applications or systems designed to integrate NOVOSENSE's products. No license to any intellectual property rights of NOVOSENSE is granted by implication or otherwise. Using this Document for any other purpose, or any unauthorized reproduction or display of this Document is strictly prohibited. In no event shall NOVOSENSE be liable for any claims, damages, costs, losses or liabilities arising out of or in connection with this Document or the use of this Document.

For further information on applications, products and technologies, please contact NOVOSENSE (www.novosns.com).

Suzhou NOVOSENSE Microelectronics Co., Ltd