# **High-speed CAN Transceiver**

Datasheet (EN) 1.0

#### **Product Overview**

The NCA1043B high-speed CAN transceiver provides an interface between a Controller Area Network (CAN) protocol controller and the physical two-wire CAN bus. The transceiver is designed for high-speed CAN applications in the automotive industry, providing differential transmit and receive capability to (a microcontroller with) a CAN protocol controller.

The NCA1043B offers excellent Electro Magnetic Compatibility (EMC) and Electro Static Discharge (ESD) performance, very low power consumption, and passive behavior when the supply voltage is turned off.

These features make the NCA1043B the ideal choice for high-speed CAN networks containing nodes that need to be available all times, even when the internal  $V_{10}$  and  $V_{CC}$  supplies are switched off.

### **Key Features**

- Fully compatible with the ISO11898-2 standard and SAE J2284-1 to SAE J2284-5

- I/O voltage range supports 3V and 5V MCU

- Bus fault protection of -58V to +58V

- Transmit data (TXD) dominant time out function

- Bus dominant time out function

- Low-power management controls the power supply throughout the node while supporting local and remote wake-up with wake-up source recognition

- Several protection and diagnostic functions including bus line short-circuit detection and battery connection detection

- CAN FD Date rate: up to 5Mbps

- Low loop delay: <250ns</li>

- Operation temperature: -40 °C ~125 °C

- AEC-Q100 qualified for automotive applications

- RoHS-compliant packages: SOP14, DFN14

### **Applications**

- 12-V or 24-V System applications

- Automotive and transportation

- Advanced driver assistance system (ADAS)

- Infotainment

- Cluster

- Body electronics & lighting

#### **Device Information**

| Part Number     | Package | Body Size       |

|-----------------|---------|-----------------|

| NCA1043B-Q1SPKR | SOP14   | 8.63mm × 3.90mm |

| NCA1043B-Q1DNKR | DFN14   | 4.50mm × 3.00mm |

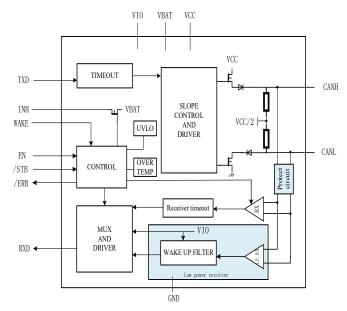

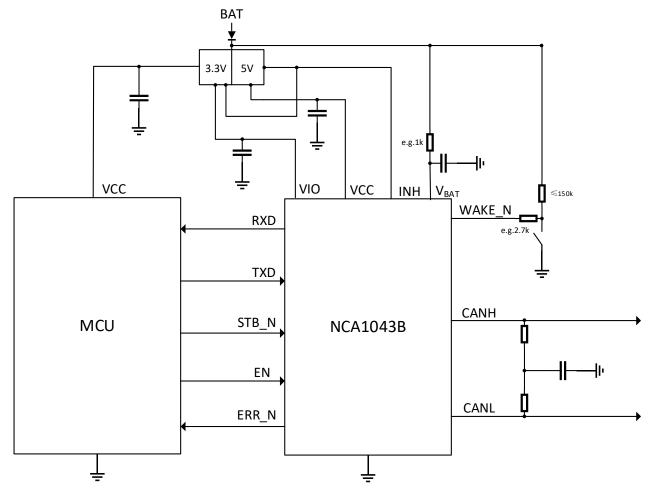

### **Functional Block Diagrams**

Figure 1 NCA1043B Block Diagram

### **INDEX**

| 1. PIN CONFIGURATION AND FUNCTIONS        | 3  |

|-------------------------------------------|----|

| 2. ABSOLUTE MAXIMUM RATINGS               | 4  |

| 3. ESD RATINGS                            | 4  |

| 4. RECOMMENDED OPERATING CONDITIONS       | E  |

|                                           |    |

| 5. THERMAL INFORMATION                    | 5  |

| 5. SPECIFICATIONS                         | 5  |

| 6.1. Static Characteristics               | 5  |

| 6.2. DYNAMIC CHARACTERISTICS              |    |

| 6.3. PARAMETER MEASUREMENT INFORMATION    | 10 |

| 6.4. Typical Performance Characteristics  | 12 |

| 7. FUNCTION DESCRIPTION                   | 13 |

|                                           |    |

| 7.1. OPERATING MODES                      |    |

| 7.1.2. Listen-only mode                   |    |

| 7.1.3. Standby mode                       |    |

| 7.1.4. Go-to-Sleep mode                   |    |

| 7.1.5. Sleep mode                         |    |

| 7.2. INTERNAL FLAGS                       |    |

| 7.2.1. UV <sub>NOM</sub> flag             |    |

| 7.2.2. UV <sub>BAT</sub> flag             | 15 |

| 7.2.3. Pwon flag                          | 15 |

| 7.2.4. Wake flag                          |    |

| 7.2.5. Remote wake-up (via the CAN bus)   |    |

| 7.2.6. Wake-up source flag                |    |

| 7.2.7. Bus failure flag                   |    |

| 7.2.8. Local failure flag                 |    |

| 7.3. LOCAL FAILURES                       |    |

| 7.3.1. TXD dominant time-out function     |    |

| 7.3.2. TXD-to-RXD short-circuit detection |    |

| 7.3.4. Overtemperature detection          |    |

| 7.3.4. VIO SUPPLY PIN                     |    |

| 7.5. WAKE PIN                             |    |

| 3. APPLICATION NOTE                       |    |

|                                           |    |

| 8.1. TYPICAL APPLICATION CIRCUIT          |    |

| 9. PACKAGE INFORMATION                    | 19 |

| 10. ORDERING INFORMATION                  | 21 |

| 11. TAPE AND REEL INFORMATION             | 22 |

| 12. REVISION HISTORY                      | 24 |

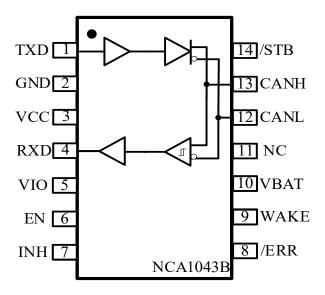

## 1. Pin Configuration and Functions

Figure 1.1 NCA1043B Package

Table 1.1 NCA1043B Pin Configuration and Description

| NSI8266W PIN<br>NO. | SYMBOL | FUNCTION                                                                                            |

|---------------------|--------|-----------------------------------------------------------------------------------------------------|

| 1                   | TXD    | CAN transmit data input (Internal weak pull-up ,LOW for dominant and HIGH for recessive bus states) |

| 2                   | GND    | Ground                                                                                              |

| 3                   | VCC    | Power Supply                                                                                        |

| 4                   | RXD    | CAN receive data output (LOW for dominant and HIGH for recessive bus states)                        |

| 5                   | VIO    | Logic I/O supply voltage                                                                            |

| 6                   | EN     | enable control input (Internal weak pull-down)                                                      |

| 7                   | INH    | inhibit output for switching external voltage regulators                                            |

| 8                   | /ERR   | error and power-on indication output (active LOW)                                                   |

| 9                   | WAKE   | local wake-up input (Internal weak pull-up and down)                                                |

| 10                  | VBAT   | battery supply voltage                                                                              |

| 11                  | NC     | No connection                                                                                       |

| 12                  | CANL   | Low-level CAN bus line                                                                              |

| 13                  | CANH   | High-level CAN bus line                                                                             |

| 14                  | /STB   | STB (standby mode) select pin (active LOW, Internal weak pull-down)                                 |

## 2. Absolute Maximum Ratings

| Parameters                            | Symbol                                | Min  | Тур | Max | Unit       | Comments                                                |

|---------------------------------------|---------------------------------------|------|-----|-----|------------|---------------------------------------------------------|

| Power Supply Voltage                  | V <sub>CC</sub> , V <sub>IO</sub>     | -0.3 |     | 7   | V          |                                                         |

| Power Supply Voltage                  | $V_{BAT}$                             | -0.3 |     | 58  | V          |                                                         |

| I/O Voltage                           | TXD, RXD,<br>STB_N, EN,<br>ERR_N      | -0.3 |     | 7   | V          |                                                         |

| 1/O voltage                           | INH and WAKE                          | -0.3 |     | 58  | V          |                                                         |

|                                       | V <sub>CANH</sub> , V <sub>CANL</sub> | -58  |     | 58  | V          |                                                         |

| Voltage Between pin CANH and pin CANL | V <sub>(CANH-CANL)</sub>              | -58  |     | 58  | V          |                                                         |

| Current on pin WAKE                   | Iwake                                 | -15  |     |     | mA         |                                                         |

|                                       |                                       | -100 |     |     | V          | On pin CANH and CANL,<br>VBAT,<br>ISO 7637- 3 pulses 1  |

| Transient Veltege                     | $V_{trt}$                             |      |     | 75  | V          | On pin CANH and CANL,<br>VBAT,<br>ISO 7637- 3 pulses 2a |

| Transient Voltage                     |                                       | -150 |     |     | V          | On pin CANH and CANL,<br>VBAT,<br>ISO 7637- 3 pulses 3a |

|                                       |                                       |      |     | 100 | V          | On pin CANH and CANL,<br>VBAT,<br>ISO 7637- 3 pulses 3b |

| Junction Temperature                  | Tj                                    | -40  |     | 150 | $^{\circ}$ |                                                         |

| Storage Temperature                   | $T_{stg}$                             | -65  |     | 150 | $^{\circ}$ |                                                         |

## 3. ESD Ratings

|                         | Ratings                                                          | Value     | Unit |

|-------------------------|------------------------------------------------------------------|-----------|------|

|                         | Human body model (HBM), per AEC-Q100-002-RevD                    |           |      |

|                         | CANH,CANL to GND                                                 | $\pm$ 8.0 | kV   |

|                         | Other pins                                                       | ±4.0      | kV   |

| Electrostatic discharge | Charged device model (CDM), per AEC-Q100-011-RevB                |           |      |

|                         | All pins                                                         | ±2.0      | kV   |

|                         | System, per IEC 61000 4 2 (150 pF, 330 $\Omega$ at pins CANH and | ±8.0      | kV   |

| CANL to GND |  |  |

|-------------|--|--|

|-------------|--|--|

## **4. Recommended Operating Conditions**

| Parameters                   | Symbol          | Min     | Тур | Max     | unit       |

|------------------------------|-----------------|---------|-----|---------|------------|

| Power Supply Voltage         | $V_{BAT}$       | 4.5     |     | 40      | V          |

|                              | Vcc             | 4.5     |     | 5.5     | V          |

|                              | V <sub>IO</sub> | 2.8     |     | 5.5     | V          |

| TXD High level input voltage | $V_{IH(TXD)}$   | 0.7*VIO |     | VIO+0.3 | V          |

| TXD Low level input voltage  | $V_{IL(TXD)}$   | -0.3    |     | 0.3*VIO | V          |

| RXD Output High current      | Іон             | -12     |     | -1      | mA         |

| RXD Output Low current       | loL             | 2       |     | 14      | mA         |

| Operating Temperature        | $T_{opr}$       | -40     |     | 125     | $^{\circ}$ |

## 5. Thermal Information

| Parameters                                | Symbol               | SOP14 | DFN14 | Unit |

|-------------------------------------------|----------------------|-------|-------|------|

| IC Junction-to-Air Thermal Resistance     | $	heta_{JA}$         | 78    | 33.1  | °C/W |

| Junction-to-case (top) thermal resistance | $\theta_{JC\ (top)}$ | 33.6  | 30.5  | °C/W |

| Junction-to-board thermal resistance      | θ <sub>ЈВ</sub>      | 34.7  | 10.8  | °C/W |

## 6. Specifications

### **6.1. Static Characteristics**

$(VCC=4.5V\sim5.5V, VIO=2.8V\sim5.5V, VBAT4.5V\sim40V, Ta=-40^{\circ}C \text{ to } 125^{\circ}C. Unless otherwise noted, Typical values are at VCC=5V, VIO=3.3V, VBAT=12V, Ta=25^{\circ}C)$

| Parameters                | Symbol                       | Min | Тур | Max | Unit | Comments                                   |

|---------------------------|------------------------------|-----|-----|-----|------|--------------------------------------------|

|                           | V <sub>cc</sub>              | 4.5 |     | 5.5 | V    |                                            |

|                           | $V_{\text{uvd(VCC)}}$        | 3   |     | 4.3 | V    | undervoltage detection voltage on pin VCC  |

|                           | $V_{IO}$                     | 2.8 |     | 5.5 | V    |                                            |

| Supply Voltage            | $V_{\text{uvd}(\text{VIO})}$ | 0.8 |     | 2.5 | V    | undervoltage detection voltage on pin VIO  |

|                           | $V_{BAT}$                    | 4.5 |     | 40  | V    |                                            |

|                           | $V_{uvd(VBAT)}$              | 3   |     | 4.3 | V    | undervoltage detection voltage on pin VBAT |

| supply current on pin VCC | Icc                          |     |     | 65  | mA   | TXD=0, R₁=60Ω, Normal mode                 |

| Parameters                    | Symbol           | Min                 | Тур | Max                  | Unit       | Comments                                                                                                  |

|-------------------------------|------------------|---------------------|-----|----------------------|------------|-----------------------------------------------------------------------------------------------------------|

|                               |                  |                     |     | 109                  | mA         | Normal mode, TXD=0,short circuit<br>on bus lines:<br>-3V<(V <sub>CANH</sub> =V <sub>CANL</sub> ) <18V     |

|                               |                  |                     |     | 9                    | mA         | TXD=V <sub>IO</sub> , Normal mode or Listen only mode                                                     |

|                               |                  |                     |     | 3.5                  | uA         | Standby or Sleep mode                                                                                     |

|                               |                  |                     |     | 350                  | uA         | Normal mode, TXD=0, R <sub>L</sub> =60Ω                                                                   |

| supply current on pin VIO     | l <sub>io</sub>  |                     |     | 4                    | uA         | TXD=V <sub>10</sub> , Normal or Listen only mode                                                          |

|                               |                  |                     |     | 4                    | uA         | Standby or Sleep mode                                                                                     |

|                               |                  |                     |     | 50                   | uA         | Normal or Listen only mode                                                                                |

| supply current on pin<br>VBAT | I <sub>BAT</sub> |                     | 18  | 40                   | uA         | Standby mode, V <sub>INH</sub> =V <sub>WAKE</sub> =V <sub>BAT</sub> , VCC>4.5V                            |

|                               |                  |                     | 18  | 40                   | uA         | Sleep mode,<br>V <sub>INH</sub> =V <sub>CC</sub> =V <sub>IO</sub> =0, V <sub>WAKE</sub> =V <sub>BAT</sub> |

| Thermal-Shutdown<br>Threshold | T <sub>TS</sub>  |                     | 190 |                      | $^{\circ}$ |                                                                                                           |

| Logic Side                    |                  |                     |     |                      | -          |                                                                                                           |

| High level input voltage      | V <sub>IH</sub>  | 0.7*V <sub>IO</sub> |     | V <sub>10</sub> +0.3 | V          | TXD &STB_N, EN pin                                                                                        |

| Low level input voltage       | V <sub>IL</sub>  | -0.3                |     | 0.3*V <sub>IO</sub>  | V          | TXD &STB_N, EN pin                                                                                        |

| High level input current      | I <sub>IH</sub>  | -5                  |     | 5                    | uA         | TXD pin, V <sub>IN</sub> =V <sub>IO</sub>                                                                 |

| High level input current      | I <sub>IH</sub>  | 1                   |     | 10                   | uA         | STB_N, EN pin, V <sub>IN</sub> =V <sub>IO</sub>                                                           |

| Low level input current       | I <sub>IL</sub>  | -260                |     | -30                  | uA         | TXD pin, TXD=0                                                                                            |

| Low level input current       | IιL              | -1                  |     | 1                    | uA         | STB_N, EN pin, V <sub>IN</sub> =0                                                                         |

| Output High current           | Іон              | -12                 | -3  | -1                   | mA         | RXD=V <sub>IO</sub> -0.4V                                                                                 |

| Output High current           | ТОН              | -50                 |     | -4                   | uA         | ERR_N=V <sub>IO</sub> -0.4, V <sub>IO</sub> =V <sub>CC</sub>                                              |

| Output Low current            | ,                | 2                   | 5   | 14                   | mA         | RXD=0.4V                                                                                                  |

| Output Low current            | loL              | 0.1                 |     | 2                    | mA         | ERR_N=0.4V                                                                                                |

| Input Capacitance             | C <sub>IN</sub>  |                     | 2   |                      | pF         | TXD pin, Not tested in production, guaranteed by design.                                                  |

| WAKE                          | <del>,</del>     |                     |     |                      |            |                                                                                                           |

| High level Input current      | Іін              | -10                 |     | -1                   | uA         | V <sub>WAKE</sub> =V <sub>BAT</sub> -1.9V                                                                 |

| Low level Input current       | Iιι              | 1                   |     | 10                   | uA         | V <sub>WAKE</sub> =V <sub>BAT</sub> -3.1V                                                                 |

| Threshold voltage             | $V_{th}$         | V <sub>BAT</sub> -3 |     | V <sub>BAT</sub> -2  | V          | V <sub>STB_N</sub> =0                                                                                     |

| Parameters                                  | Symbol              | Min    | Тур               | Max    | Unit | Comments                                                                                                                                                         |

|---------------------------------------------|---------------------|--------|-------------------|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INH                                         |                     |        |                   |        |      |                                                                                                                                                                  |

| High level voltage drop                     | $\Delta V_H$        | 0      |                   | 0.8    | V    | I <sub>INH</sub> =-0.18mA                                                                                                                                        |

| Leakage current                             | I <sub>L</sub>      | -2     |                   | 2      | uA   | Sleep mode                                                                                                                                                       |

| Driver                                      |                     |        |                   | •      |      |                                                                                                                                                                  |

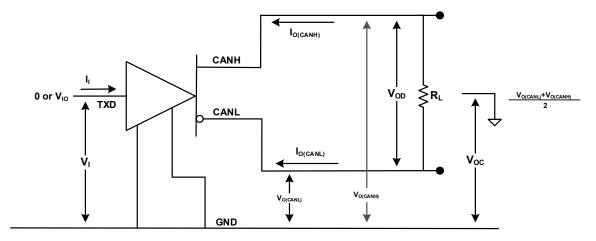

| CANH output voltage<br>(Dominant)           | V <sub>OH(D)</sub>  | 2.75   |                   | 4.5    | V    | $V_{TXD}$ =0V, $R_{Load}$ =50 to $65\Omega$                                                                                                                      |

| CANL output voltage<br>(Dominant)           | V <sub>OL(D)</sub>  | 0.5    |                   | 2.25   | V    | $V_{TXD}$ =0V, $R_{Load}$ =50 to 65 $\Omega$                                                                                                                     |

| Transmitter dominant voltage symmetry       | $V_{dom(TX)sym}$    | -400   |                   | 400    | mV   | $V_{dom(TX)sym} = V_{CC} - V_{CANH} - V_{CANL}$                                                                                                                  |

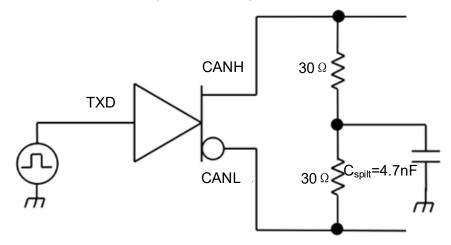

| transmitter voltage<br>symmetry             | V <sub>TXsym</sub>  | 0.9VCC |                   | 1.1VCC | V    | $V_{TXsym} = V_{CANH} + V_{CANL}$ $f_{TXD} = 250 \text{ kHz}, 1 \text{ MHz and } 2.5 \text{ MHz}$ Not tested in production, guaranteed by design. See Figure 6.5 |

| CAN bus output voltage                      | $V_{O(R)}$          | 2      | 05V <sub>cc</sub> | 3      | V    | Normal or Listen-only mode, $V_{TXD}=V_{IO}$ , no load                                                                                                           |

| (Recessive)                                 | - (,,               | -0.1   |                   | 0.1    | V    | Standby or Sleep mode, no load                                                                                                                                   |

|                                             |                     | 1.5    |                   | 3      | V    | $V_{TXD}$ =0V, $R_{Load}$ =45 to 65 $\Omega$                                                                                                                     |

| Differential output voltage (Dominant)      | V <sub>OD(D)</sub>  | 1.5    |                   | 3.3    | V    | $V_{TXD}$ =0V, $R_{Load}$ =45 to $70\Omega$                                                                                                                      |

|                                             |                     | 1.5    |                   | 5      |      | $V_{TXD}$ =0V, $R_{Load}$ =2240 $\Omega$                                                                                                                         |

| Differential output voltage (Recessive)     | V <sub>OD(R)</sub>  | -50    |                   | 50     | mV   | Normal or listen only mode,<br>VTXD=VIO                                                                                                                          |

|                                             |                     | -0.2   |                   | 0.2    | V    | Standby or sleep mode                                                                                                                                            |

| Common-mode output voltage                  | Voc                 | 2      | 05V <sub>CC</sub> | 3      | V    |                                                                                                                                                                  |

| Peak-to-peak Common-<br>mode output voltage | V <sub>OC(PP)</sub> |        | 250               |        | mV   |                                                                                                                                                                  |

|                                             |                     | -100   |                   | -40    | mA   | Test CANH, TXD=0, V <sub>CANH</sub> =-15V to +40 V                                                                                                               |

| Short- circuit output current               | los                 | 40     |                   | 100    | mA   | Test CANL, TXD=0, V <sub>CANL</sub> =-15 V to +40 V                                                                                                              |

|                                             |                     | -3     |                   | 3      | mA   | Normal mode; $V_{TXD}=V_{IO}$ ; $V_{CANH}=V_{CANL}=-27 \text{ V to } +32 \text{ V}$                                                                              |

| Receiver                                    |                     |        |                   | •      | •    | •                                                                                                                                                                |

| Parameters                       | Symbol              | Min  | Тур | Max  | Unit | Comments                                                                                                              |

|----------------------------------|---------------------|------|-----|------|------|-----------------------------------------------------------------------------------------------------------------------|

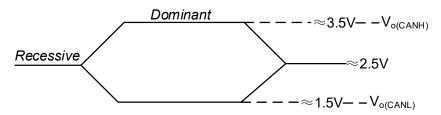

| differential receiver            | $V_{th(RX)dif}$     | 0.5  |     | 0.9  | V    | -30 V <v<sub>CANL&lt;+30 V; -30 V<v<sub>CANH&lt;+30 V; normal or listen only mode</v<sub></v<sub>                     |

| threshold voltage                | <b>V</b> th(RX)dif  | 0.4  |     | 1.15 | V    | -30 V <v<sub>CANL&lt;+30 V; -30V<v<sub>CANH&lt;+30 V; standby or sleep mode</v<sub></v<sub>                           |

| receiver recessive voltage       | V con               | -4   |     | 0.5  | V    | -30 V <v<sub>CANL&lt;+30 V; -30 V<v<sub>CANH&lt;+30 V; normal or listen only mode</v<sub></v<sub>                     |

| receiver recessive voltage       | $V_{\sf rec(RX)}$   | -4   |     | 0.4  | V    | -30V <v<sub>CANL&lt;+30 V; -30V<v<sub>CANH&lt;+30 V;<br/>standby or sleep mode</v<sub></v<sub>                        |

| receiver dominant                | $V_{ m dom(RX)}$    | 0.9  |     | 9    | V    | -30 V <v<sub>CANL&lt;+30 V; -30<br/>V<vcanh<+30 listen<br="" normal="" or="" v;="">only mode</vcanh<+30></v<sub>      |

| voltage                          | <b>V</b> dom(RX)    | 1.15 |     | 9    | V    | -30 V <vcanl<+30 -<br="" v;="">30V<vcanh<+30 or<br="" standby="" v;="">sleep mode</vcanh<+30></vcanl<+30>             |

| Hysteresis voltage               | V <sub>HYS</sub>    |      | 50  |      | mV   | -30 V <v<sub>CANL&lt;+30 V, -30 V<v<sub>CANH&lt;+30 V normal or listen only mode</v<sub></v<sub>                      |

|                                  |                     | 100  |     | 400  | uA   | $V_{CANH} = V_{CANL} = 5 \text{ V}, V_{CC} = 0 \text{ V}$                                                             |

| Power-off (unpowered)            |                     | -2   |     | 8    | uA   | V <sub>CANH</sub> = V <sub>CANL</sub> = 5 V, V <sub>BAT</sub> = 0V                                                    |

| bus input leakage current        | Hoff(LKG)           | -2   |     | 8    | uA   | $V_{CC}=V_{IO}=V_{BAT}=0$ V or $V_{CC}=V_{IO}=V_{BAT}=s$ horted to ground via 47 k $\Omega$ ; $V_{CANH}=V_{CANL}=5$ V |

| common-mode input<br>capacitance | Cı                  |      |     | 20   | pF   | guaranteed by design                                                                                                  |

| Differential input capacitance   | C <sub>ID</sub>     |      |     | 10   | pF   | guaranteed by design                                                                                                  |

| Differential input resistance    | $R_{\text{ID}}$     | 18   | 30  | 56   | kΩ   | -2V <v<sub>CANL&lt;+7V,<br/>-2V<v<sub>CANH&lt;+7V;</v<sub></v<sub>                                                    |

| Input resistance                 | R <sub>IN</sub>     | 9    | 15  | 28   | kΩ   | -2 V <v<sub>CANL&lt;+7 V,<br/>-2V<v<sub>CANH&lt;+7 V;</v<sub></v<sub>                                                 |

| Input resistance<br>matching     | R <sub>Imatch</sub> | -3   |     | +3   | %    | 0 V <v<sub>CANL&lt;+5 V,<br/>0V<v<sub>CANH&lt;+5 V;</v<sub></v<sub>                                                   |

| Common-mode voltage range        | V <sub>CM</sub>     | -30  |     | +30  | V    |                                                                                                                       |

### **6.2. Dynamic Characteristics**

$(VCC=4.5V\sim5.5V, VIO=2.8V\sim5.5V, VBAT4.5V\sim40V, Ta=-40^{\circ}C\ to\ 125^{\circ}C.\ Unless\ otherwise\ noted, Typical\ values\ are\ at\ VCC=5V,\ VIO=3.3V,\ VBAT=12V,\ Ta=25^{\circ}C)$

| Parameters                              | Symbol                     | Min  | Тур | Max | Unit | Comments                                                                                  |  |

|-----------------------------------------|----------------------------|------|-----|-----|------|-------------------------------------------------------------------------------------------|--|

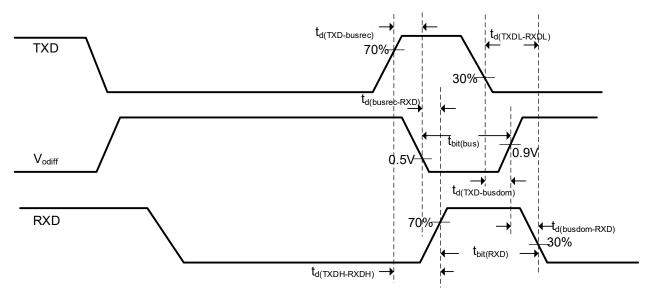

| delay time from TXD Low<br>to RXD Low   | t <sub>d(TXDL-RXDL)</sub>  | 40   |     | 240 | ns   | Driver input to receiver output,<br>Recessive to Dominant, normal<br>mode, see Figure 6.4 |  |

| delay time from TXD High<br>to RXD High | t <sub>d(TXDH-RXDH)</sub>  | 40   |     | 240 | ns   | Driver input to receiver output,<br>Dominant to Recessive, normal<br>mode, see Figure 6.4 |  |

| undervoltage detection<br>time          | t <sub>det(uv)</sub>       | 100  |     | 350 | ms   | guaranteed by design                                                                      |  |

| undervoltage recovery<br>time           | t <sub>rec(uv)</sub>       | 1    |     | 5   | ms   | guaranteed by design                                                                      |  |

| transmitted recessive bit               | t <sub>bit(bus)</sub>      | 435  |     | 530 | ns   | t <sub>bit(TXD)</sub> = 500 ns, see Figure 6.4                                            |  |

| width                                   |                            | 155  |     | 210 | ns   | t <sub>bit(TXD)</sub> = 200 ns, see Figure 6.4                                            |  |

| bit time on pin RXD                     | t <sub>bit(RXD)</sub>      | 400  |     | 550 | ns   | t <sub>bit(TXD)</sub> = 500 ns, see Figure 6.4                                            |  |

|                                         |                            | 120  |     | 220 | ns   | t <sub>bit(TXD)</sub> = 200 ns, see Figure 6.4                                            |  |

| delay time from TXD to<br>bus dominant  | $t_{d(TXD	ext{-}busdom)}$  |      | 65  |     | ns   | Normal mode. see Figure 6.4                                                               |  |

| delay time from TXD to<br>bus recessive | td <sub>(TXD-busres)</sub> |      | 70  |     | ns   | Normal mode, see Figure 6.4                                                               |  |

| delay time from bus<br>dominant to RXD  | t <sub>d(busdom-RXD)</sub> |      | 80  |     | ns   | Normal or listen only mode, see<br>Figure 6.4                                             |  |

| delay time from bus recessive to RXD    | t <sub>d(busres-RXD)</sub> |      | 90  |     | ns   | Normal or listen only mode, see<br>Figure 6.4                                             |  |

| Receiver timing                         | $\Delta t_{rec}$           | -65  |     | 40  | ns   | t <sub>bit(TXD)</sub> = 500 ns                                                            |  |

| symmetry                                |                            | -45  |     | 15  | ns   | t <sub>bit(TXD)</sub> = 200 ns                                                            |  |

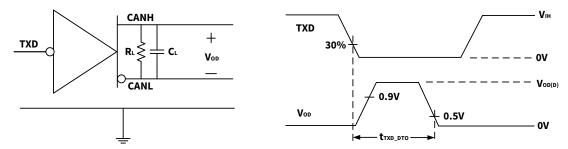

| TXD dominant time-out time              | t <sub>TXD_DTO</sub>       | 0.35 |     | 1.5 | ms   | V <sub>TXD</sub> = 0 V; Normal mode                                                       |  |

| Bus dominant time out time              | t <sub>bus_DTO</sub>       | 0.35 |     | 1.5 | ms   | Listen-only mode                                                                          |  |

| hold time                               | th                         | 20   |     | 120 | us   | from issuing go-to-sleep command to entering Sleep mode                                   |  |

| bus dominant wake-up<br>time            | t <sub>wake(busdom)</sub>  | 0.5  |     | 3.5 | us   | Standby or Sleep mode,<br>V <sub>BAT</sub> = 12 V                                         |  |

| bus recessive wake-up<br>time           | twake(busres)              | 0.5  |     | 3.5 | us   | Standby or Sleep mode,<br>V <sub>BAT</sub> = 12 V                                         |  |

| bus wake-up timeout<br>time             | t <sub>to(wake)</sub> bus  | 0.5  |     | 2   | ms   | bus wake-up filter time                                                                   |  |

| Parameters  | Symbol            | Min | Тур | Max | Unit | Comments                                                                         |

|-------------|-------------------|-----|-----|-----|------|----------------------------------------------------------------------------------|

| Wakeup time | t <sub>wake</sub> | 5   |     | 100 | us   | in response to a falling or rising<br>edge on pin WAKE; Standby or<br>Sleep mode |

#### 6.3. Parameter Measurement Information

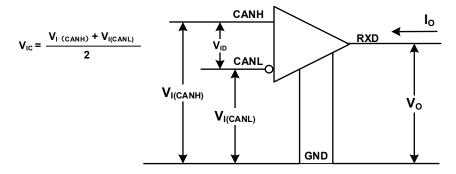

Figure 6.1 Driver Voltage, Current and Test Definitions

Figure 6.2 Bus Logic State Voltage Definitions

Figure 6.3 Receiver Voltage and Current Definitions

Figure 6.4 CAN timing definitions

Figure 6.5 Transceiver Driver Symmetry Test Circuit

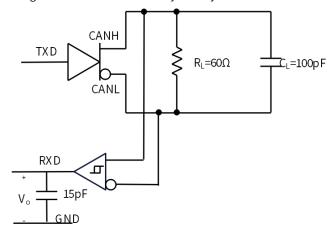

Figure 6.6 Timing test circuit

Figure 6.7 TXD Dominant Time Out Test Circuit and Measurement

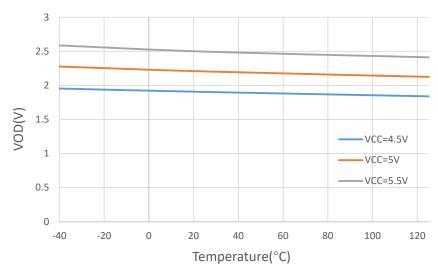

### **6.4. Typical Performance Characteristics**

Figure 6.8  $V_{OD(D)}$  vs temperature ( $R_{Load} = 60\Omega$ )

## 7. Function Description

The NCA1043B is a stand-alone high-speed CAN transceiver with a number of operating modes, fail-safe features and diagnostic features that offer enhanced system reliability and advanced power management. The transceiver has excellent EMC and ESD capability and quiescent current capability. Slope control and high DC handling capability on the bus pins provide additional application flexibility.

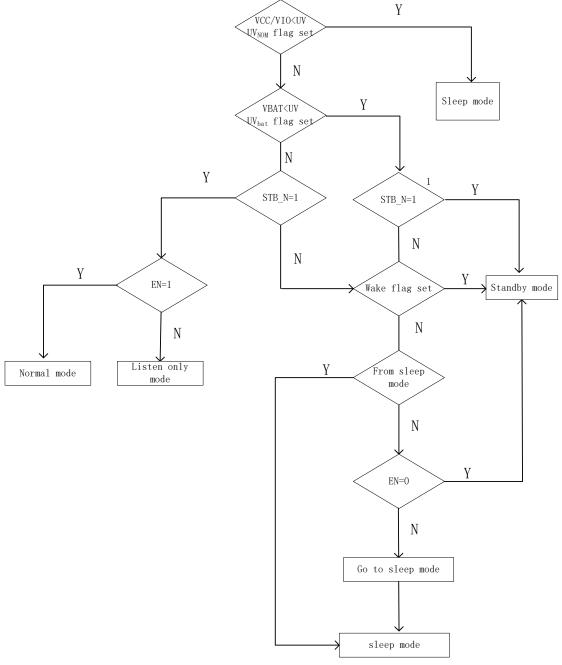

### 7.1. Operating modes

The NCA1043B supports five operating modes. Control pins STB\_N and EN are used to select the operating mode. Switching between modes allows access to a number of diagnostics flags via pin ERR\_N. Figure 7.1 and Table 7.1 describes how to switch between modes.

Figure 7.1 Mode transition

Note1: The mode switching is in the precondition of UV<sub>BAT</sub> is set.

| Internal flags |                                                         |         | Contro | ol pins | Operating mode   | INH      |  |  |  |

|----------------|---------------------------------------------------------|---------|--------|---------|------------------|----------|--|--|--|

| $UV_{NOM}$     | $UV_{BAT}$                                              | Wake    | STB_N  | EN      |                  |          |  |  |  |

| From Norm      | From Normal, Listen-only, Standby and Go-to-Sleep modes |         |        |         |                  |          |  |  |  |

| set            | ×                                                       | ×       | ×      | ×       | Sleep mode       | floating |  |  |  |

| cleared        | set                                                     | ×       | High   | ×       | Standby mode     | High     |  |  |  |

| cleared        | ×                                                       | set     | Low    | ×       | Standby mode     | High     |  |  |  |

| cleared        | ×                                                       | cleared | Low    | Low     | Standby mode     | High     |  |  |  |

| cleared        | ×                                                       | cleared | Low    | High    | Go-to-Sleep mode | High     |  |  |  |

| cleared        | cleared                                                 | ×       | High   | Low     | Listen-only mode | High     |  |  |  |

| cleared        | cleared                                                 | ×       | High   | High    | Normal mode      | High     |  |  |  |

| From Sleep     | mode                                                    |         |        |         |                  |          |  |  |  |

| set            | ×                                                       | ×       | ×      | ×       | Sleep mode       | floating |  |  |  |

| cleared        | set                                                     | ×       | High   | ×       | Standby mode     | High     |  |  |  |

| cleared        | ×                                                       | set     | Low    | ×       | Standby mode     | High     |  |  |  |

| cleared        | ×                                                       | cleared | Low    | ×       | Sleep mode       | floating |  |  |  |

| cleared        | cleared                                                 | ×       | High   | Low     | Listen-only mode | High     |  |  |  |

| cleared        | cleared                                                 | ×       | High   | High    | Normal mode      | High     |  |  |  |

Table 7.1 Operating mode selection

#### 7.1.1. Normal mode

In Normal mode, the transceiver can transmit and receive data via the bus lines CANH and CANL (see Figure 1 for the block diagram). The differential receiver converts the analog data on the bus lines into digital data which is output to pin RXD. The slopes of the output signals on the bus lines are controlled internally and are optimized in a way that guarantees the lowest possible EME. The bus pins are biased to 0.5V<sub>CC</sub> (via R<sub>i</sub>). Pin INH is active, so voltage regulators controlled by pin INH will be active too.

#### 7.1.2. Listen-only mode

In Listen-only mode, the transceiver's transmitter is disabled, effectively providing a transceiver listen-only feature. The receiver will still convert the analog bus signal on pins CANH and CANL into digital data, available for output on pin RXD. As in Normal mode, the bus pins are biased at 0.5V<sub>CC</sub> and pin INH remains active.

#### 7.1.3. Standby mode

Standby mode is the NCA1043B's first-level power saving mode, offering reduced current consumption. In Standby mode, the transceiver is unable to transmit or receive data and the low-power receiver is activated to monitor bus activity. The bus pins are biased at ground level (via R<sub>i</sub>). Pin INH is still active, so voltage regulators controlled by this pin will also be active.

Pins RXD and ERR\_N will reflect any active wake-up requests (provided that V<sub>IO</sub> and V<sub>BAT</sub> are present).

#### 7.1.4.Go-to-Sleep mode

Go-to-Sleep mode is the controlled route for entering Sleep mode. In Go-to-Sleep mode, the transceiver behaves as in Standby mode, with the addition that a go-to-sleep command is issued to the transceiver. The transceiver will remain in Go-to-Sleep mode for the minimum hold time  $(t_{h(min)})$  before entering Sleep mode. The transceiver will not enter Sleep mode if the state of pin STB\_N or pin EN is changed or if the Wake flag is set before  $t_{h(min)}$  has elapsed.

#### 7.1.5.Sleep mode

Sleep mode is entered via Go-to-Sleep mode, and also when the undervoltage detection time on either  $V_{CC}$  or  $V_{IO}$  elapses before the relevant voltage level has recovered. In Sleep mode, the transceiver behaves as described for Standby mode, with the exception that pin INH is set floating. Voltage regulators controlled by this pin will be switched off, and the current into pin  $V_{BAT}$  will be reduced to a minimum. Pins STB\_N, EN and the Wake flag can be used to wake up a node from Sleep mode.

#### 7.2. Internal flags

The NCA1043B makes use of seven internal flags for its fail-safe fallback mode control and system diagnosis support. Five of these flags can be polled by the controller via pin ERR\_N. Which flag is available on pin ERR\_N at any time depends on the active operating mode and on a number of other conditions. Table 7.2 describes how to access these flags

.

| Internal flag                                               | Flag is available on pin ERR_N ¹                                                                     | Flag is cleared                                                                                                                                             |

|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UV <sub>NOM</sub>                                           | No                                                                                                   | by setting the Pwon or Wake flags, by a LOW-to-HIGH transition on STB_N or when both $V_{\text{IO}}$ and $V_{\text{BAT}}$ have recovered.                   |

| UV <sub>BAT</sub>                                           | No                                                                                                   | when V <sub>BAT</sub> has recovered                                                                                                                         |

| Pwon                                                        | in Listen-only mode (coming from Standby mode, Go-to-Sleep mode, or Sleep mode)                      | on entering Normal mode                                                                                                                                     |

| Wake                                                        | in Standby mode, Go-to-Sleep mode, and Sleep mode (provided that $V_{IO}$ and $V_{BAT}$ are present) | on entering Normal mode or by setting the $$\textsc{UV}_{\text{NOM}}$$ flag                                                                                 |

| Wake-up source                                              | in Normal mode (before the fourth dominant-to-recessive edge on pin $TXD^2$ )                        | on leaving Normal mode                                                                                                                                      |

| Bus failure                                                 | in Normal mode (after the fourth dominant-to-recessive edge on pin TXD²)                             | on re-entering Normal mode or by setting the Pwon flag                                                                                                      |

| Local failure in Listen-only mode (coming from Normal mode) |                                                                                                      | on entering Normal mode or when RXD is<br>dominant while TXD is recessive (provided<br>that all local failures are resolved) or by<br>setting the Pwon flag |

Table 7.2 Accessing internal flags via pin ERR\_N

#### 7.2.1.UV<sub>NOM</sub> flag

$UV_{NOM}$  is the  $V_{CC}$  and  $V_{IO}$  undervoltage detection flag. The flag is set when the voltage on pin  $V_{CC}$  drops below the  $V_{CC}$  undervoltage detection voltage,  $V_{uvd(VCC)}$ , for longer than the undervoltage detection time,  $t_{det(uv)}$ , or when the voltage on pin  $V_{IO}$  drops below  $V_{uvd(VIO)}$  for longer than  $t_{det(uv)}$ . When the  $UV_{NOM}$  flag is set, the transceiver enters Sleep mode to save power and to ensure the bus is not disturbed. In Sleep mode the voltage regulators connected to pin INH are disabled, avoiding any extra power consumption that might be generated as a result of a short-circuit condition.

Any wake-up request, setting the Pwon flag or a LOW-to-HIGH transition on STB\_N will clear  $UV_{NOM}$  and the timers, allowing the voltage regulators to be reactivated (at least until  $UV_{NOM}$  is set again).  $UV_{NOM}$  will also be cleared if both  $V_{CC}$  and  $V_{IO}$  recover for longer than the undervoltage recovery time,  $t_{rec(uv)}$ . The transceiver will then switch to the operating mode indicated by the logic levels on pins STB\_N and EN (see Figure 7.1 and Table 7.1).

#### 7.2.2.UV<sub>BAT</sub> flag

$UV_{BAT}$  is the  $V_{BAT}$  undervoltage detection flag. This flag is set when the voltage on pin  $V_{BAT}$  drops below  $V_{uvd(VBAT)}$ . When  $UV_{BAT}$  is set, the transceiver will try to enter Standby mode to save power and will disengage from the bus (zero load).  $UV_{BAT}$  is cleared when the voltage on pin  $V_{BAT}$  recovers. The transceiver will then switch to the operating mode indicated by the logic levels on pins STB\_N and EN (see Figure 7.1 and Table 7.1).

#### 7.2.3.Pwon flag

Pwon is the  $V_{BAT}$  power-on flag. This flag is set when the voltage on pin  $V_{BAT}$  recovers after previously dropping below  $V_{UVd(VBAT)}$  (usually because the battery was disconnected). Setting the Pwon flag clears the  $UV_{NOM}$  flag and timers. The Wake and Wake-up source flags are set to ensure consistent system power-up under all supply conditions. In Listen-only mode the Pwon flag can be polled via pin ERR\_N (see Table 7.2). The flag is cleared when the transceiver enters Normal mode.

#### 7.2.4. Wake flag

The Wake flag is set when the transceiver detects a local or remote wake-up request. A local wake-up request is detected when the logic level on pin WAKE changes, and the new level remains stable for at least  $t_{wake}$ . The Wake flag can be set in Standby mode, Goto-Sleep mode or Sleep mode. Setting the Wake flag clears the  $UV_{NOM}$  flag and timers. Once set, the Wake flag status is immediately available on pins ERR\_N and RXD (provided  $V_{IO}$  and  $V_{BAT}$  are present). This flag is also set at power-on and cleared when the  $UV_{NOM}$  flag is set or the transceiver enters Normal mode.

Pin ERR\_N is an active-LOW output, so a LOW-level indicates a set flag and a HIGH-level indicates a cleared flag. Allow pin ERR\_N to stabilize for at least 8 us after changing operating modes.

<sup>2)</sup> Allow for a TXD dominant time of at least 4 us per dominant-recessive cycle.

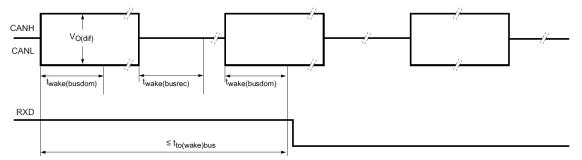

#### 7.2.5. Remote wake-up (via the CAN bus)

The NCA1043B wakes up from Standby or Sleep mode when a dedicated wake-up pattern (specified in ISO 11898-2: 2024) is detected on the bus. This filtering helps avoid spurious wake-up events. A spurious wake-up sequence could be triggered by, for example, a dominant clamped bus or by dominant phases due to noise or spikes on the bus.

The wake-up pattern consists of:

- a dominant phase of at least t<sub>wake(busdom)</sub> followed by

- a recessive phase of at least twake(busrec) followed by

- a dominant phase of at least twake(busdom)

Dominant or recessive bits between the above-mentioned phases that are shorter than  $t_{wake(busdom)}$  and  $t_{wake(busdom)}$  respectively are ignored.

The complete dominant-recessive-dominant pattern must be received within t<sub>to(wake)bus</sub> to be recognized as a valid wake-up pattern (see Figure 7.2). Otherwise, the internal wake-up logic is reset. The complete wake-up pattern will then need to be retransmitted to trigger a wake-up event. Pin RXD remains HIGH until the wake-up event has been triggered.

A wake-up event is not flagged on RXD if any of the following events occurs while a valid wake-up pattern is being received:

- The NCA1043B switches to Normal mode

- The complete wake-up pattern was not received within t<sub>to(wake)bus</sub>

- A V<sub>CC</sub> or V<sub>IO</sub> undervoltage is detected (UV<sub>NOM</sub> flag set)

Figure 7.2 Wake-up timing

#### 7.2.6. Wake-up source flag

Wake-up source recognition is provided via the Wake-up source flag, which is set when the Wake flag is set by a local wake-up request via the WAKE pin. The Wake-up source flag can be polled via the ERR\_N pin in Normal mode (see Table 7.1). This flag is also set at power-on and cleared when the transceiver leaves Normal mode.

#### 7.2.7. Bus failure flag

The Bus failure flag is set if the transceiver detects a bus line short-circuit condition to  $V_{BAT}$ ,  $V_{CC}$  or GND during four consecutive dominant-recessive cycles on pin TXD, while trying to drive the bus lines dominant. The Bus failure flag can be polled via the ERR\_N pin in Normal mode (see Table 7.1). This flag is cleared at power-on or when the transceiver re-enters Normal mode.

#### 7.2.8. Local failure flag

In Normal and Listen-only modes, the transceiver can distinguish four different local failure events, any of which will cause the Local failure flag to be set. The four local failure events are: TXD dominant clamping, TXD-to-RXD short circuit, bus dominant clamping and an overtemperature event. The nature and detection of these local failures is described in Section 7.3. The Local failure flag can be polled via the ERR\_N pin in Listen-only mode (see Table 7.1). This flag is cleared at power-on, when entering Normal mode or when RXD is dominant while TXD is recessive, provided that all local failures have been resolved.

#### 7.3. Local Failures

The NCA1043B can detect four different local failure conditions. Any of these failures will set the Local failure flag, and in most cases the transmitter of the transceiver will be disabled.

#### 7.3.1.TXD dominant time-out function

A permanent LOW level on pin TXD (due to a hardware or software application failure) would drive the CAN bus into a permanent dominant state, blocking all network communications. The TXD dominant time-out function prevents such a network lock-up by

disabling the transmitter if pin TXD remains LOW for longer than the TXD dominant time-out time  $t_{to(dom)TXD}$ . The  $t_{to(dom)TXD}$  timer defines the minimum possible bit rate of 40 kbit/s. The transmitter remains disabled until the Local failure flag has been cleared.

#### 7.3.2.TXD-to-RXD short-circuit detection

A short-circuit between pins RXD and TXD would lock the bus in a permanent dominant state once it had been driven dominant, because the low-side driver of RXD is typically stronger than the high-side driver of the controller connected to TXD. TXD-to-RXD short-circuit detection prevents such a network lock-up by disabling the transmitter. The transmitter remains disabled until the Local failure flag has been cleared.

#### 7.3.3. Bus dominant time-out function

A CAN bus short circuit (to  $V_{BAT}$ ,  $V_{CC}$  or GND) or a failure in one of the other network nodes could result in a differential voltage on the bus high enough to represent a bus dominant state. Because a node will not start transmission if the bus is dominant, the normal bus failure detection will not detect this failure, but the bus dominant clamping detection will. The Local failure flag is set if the dominant state on the bus persists for longer than  $t_{to(dom)bus}$ . By checking this flag, the controller can determine if a clamped bus is blocking network communications. There is no need to disable the transmitter. Note that the Local failure flag does not retain a bus dominant clamping failure and is released as soon as the bus returns to recessive state.

#### 7.3.4. Overtemperature detection

If the junction temperature becomes excessive, the transmitter will shut down in time to protect the output drivers from overheating without compromising the maximum operating temperature. The transmitter will remain disabled until the Local failure flag has been cleared.

#### 7.4. VIO supply pin

Pin VIO should be connected to the microcontroller supply voltage. This will cause the signal levels of pins TXD, RXD, STB\_N, EN and ERR\_N to be adjusted to the I/O levels of the microcontroller, facilitating direct interfacing without the need for glue logic.

#### 7.5. WAKE pin

A local wake-up event is triggered by a LOW-to-HIGH or HIGH-to-LOW transition on the WAKE pin, allowing for maximum flexibility when designing a local wake-up circuit. To minimize current consumption, the internal bias voltage will follow the logic state on the pin after a delay of twake. A HIGH level on pin WAKE is followed by an internal pull-up to VBAT. A LOW level on pin WAKE is followed by an internal pull-down towards GND. In applications that don't make use of the local wake-up facility, it is recommended that the WAKE pin be connected to VBAT or GND to ensure optimal EMI performance.

## 8. Application Note

### 8.1. Typical Application Circuit

Figure 8.1 Typical Application Circuit

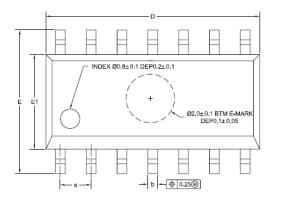

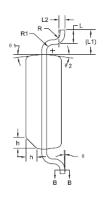

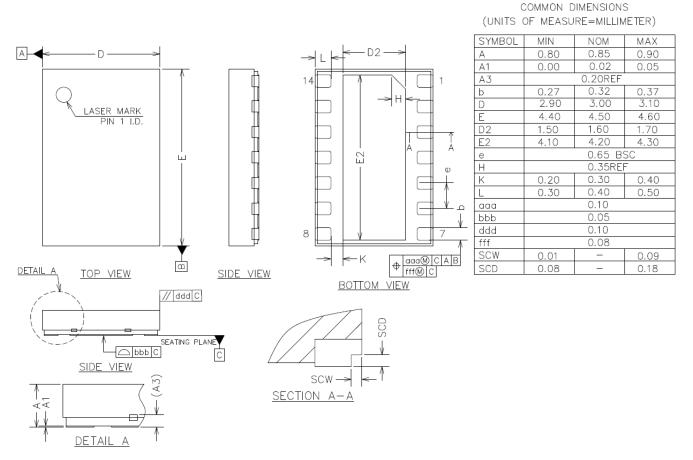

## 9. Package Information

COMMON DIMENSIONS (UNITS OF MEASURE=MILLIMETER)

| SYMBOL MIN NOM | MAN     |  |  |  |  |  |  |

|----------------|---------|--|--|--|--|--|--|

|                | MAX     |  |  |  |  |  |  |

| A 1,35 1.60    | 1,75    |  |  |  |  |  |  |

| A1 0.10 0.15   | 0.25    |  |  |  |  |  |  |

| A2 1.25 1,45   | 1.65    |  |  |  |  |  |  |

| A3 0.55 0.65   | 0.75    |  |  |  |  |  |  |

| b 0,36 -       | 0,49    |  |  |  |  |  |  |

| b1 0.35 0.40   | 0.45    |  |  |  |  |  |  |

| ∆ c 0.17 -     | 0.25    |  |  |  |  |  |  |

| ∆ c1 0.17 0.20 | 0.23    |  |  |  |  |  |  |

| D 8.53 8.63    | 8,73    |  |  |  |  |  |  |

| E 5.80 6.00    | 6.20    |  |  |  |  |  |  |

| E1 3.80 3.90   | 4.00    |  |  |  |  |  |  |

| e 1.27BSC      | 1.27BSC |  |  |  |  |  |  |

| L 0.45 0.60    | 0.80    |  |  |  |  |  |  |

| L1 1.04REF     |         |  |  |  |  |  |  |

| L2 0,25BSC     |         |  |  |  |  |  |  |

| R 0.07 -       | -       |  |  |  |  |  |  |

| R1 0.07 -      | -       |  |  |  |  |  |  |

| h 0,30 0.40    | 0,50    |  |  |  |  |  |  |

| θ 0° -         | 8°      |  |  |  |  |  |  |

| θ 1 6° 8°      | 10°     |  |  |  |  |  |  |

| θ 2 6° 8°      | 10°     |  |  |  |  |  |  |

| θ 3 5° 7°      | 9°      |  |  |  |  |  |  |

| θ 4 5° 7°      | 9°      |  |  |  |  |  |  |

Figure 9.1 SOP14 Package Shape and Dimension in millimeters

Figure 9.2 DFN14 Package Shape and Dimension in millimeters

## 10. Ordering Information

| Part Number         | Max Data Rate<br>(Mbps) | Temperature | MSL | Package<br>Type | Package<br>Drawing | SPQ  |

|---------------------|-------------------------|-------------|-----|-----------------|--------------------|------|

| NCA1043B-<br>Q1SPKR | 5                       | -40 to 125℃ | 3   | SOP14           | SOP14              | 2500 |

| NCA1043B-<br>Q1DNKR | 5                       | -40 to 125℃ | 2   | DFN14           | DFN14              | 6000 |

NOTE: All packages are RoHS-compliant with peak reflow temperatures of 260 °C according to the JEDEC industry standard classifications and peak solder temperatures.

All devices are AEC-Q100 qualified.

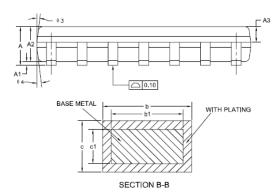

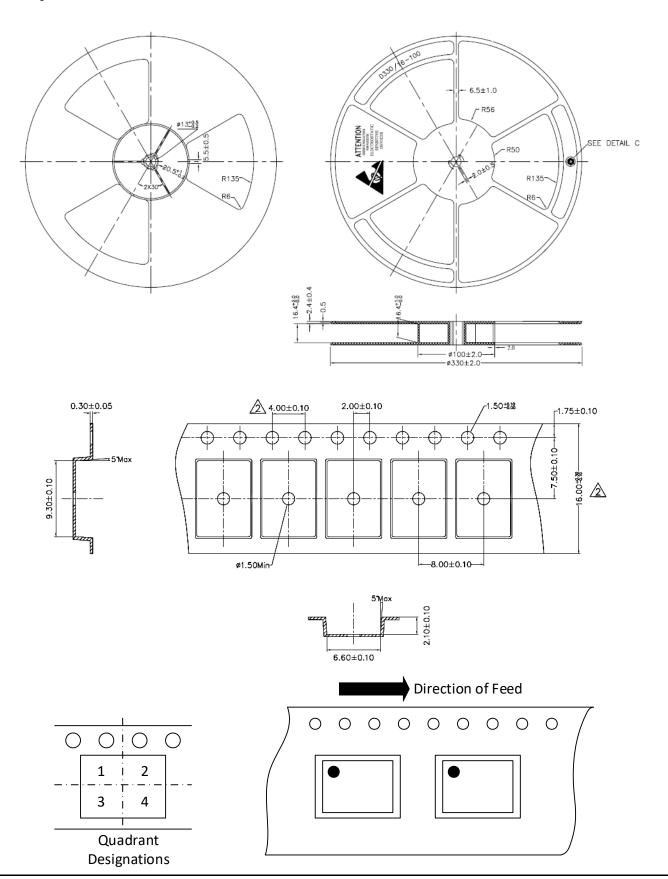

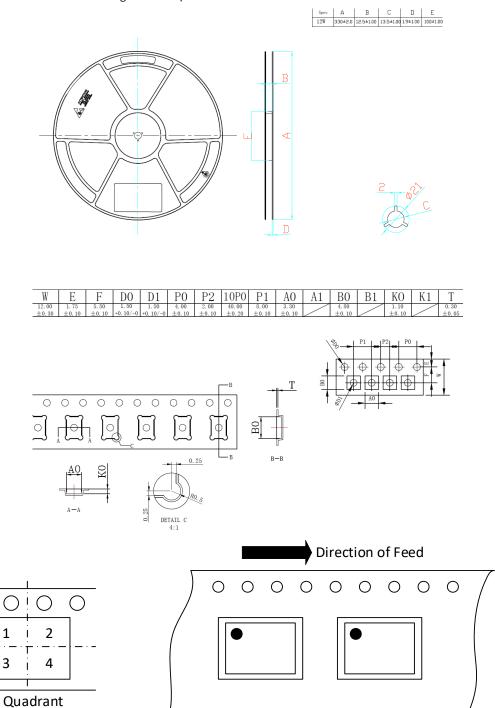

## 11. Tape and Reel Information

Figure 11.1 Tape and Reel Information of SOP14

Figure 11.2 Tape and Reel Information of DFN14

1

3

Designations

## **12. Revision History**

| Re | evision | Description      | Date      |

|----|---------|------------------|-----------|

| 1. | 0       | Initial Version. | 2024/9/11 |

#### IMPORTANT NOTICE

The information given in this document shall in no event be regarded as any warranty or authorization of, express or implied, including but not limited to accuracy, completeness, merchantability, fitness for a particular purpose or infringement of any third party's intellectual property rights.

You are solely responsible for your use of Novosense' products and applications, and for the safety thereof. You shall comply with all laws, regulations and requirements related to Novosense's products and applications, although information or support related to any application may still be provided by Novosense.

The resources are intended only for skilled developers designing with Novosense' products. Novosense reserves the rights to make corrections, modifications, enhancements, improvements or other changes to the products and services provided. Novosense authorizes you to use these resources exclusively for the development of relevant applications designed to integrate Novosense's products. Using these resources for any other purpose, or any unauthorized reproduction or display of these resources is strictly prohibited. Novosense shall not be liable for any claims, damages, costs, losses or liabilities arising out of the use of these resources.

For further information on applications, products and technologies, please contact Novosense (www.novosns.com).

Suzhou Novosense Microelectronics Co., Ltd